Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Курсовая работа: Разработка архитектуры, принципиальной схемы и конструкции специализированного микроконтроллера

Курсовая работа: Разработка архитектуры, принципиальной схемы и конструкции специализированного микроконтроллера

Введение

Микропроцессорные интегральные схемы (МП ИС) и микро-ЭВМ, построенные на их основе, явились следствием бурного развития микроэлектроники, позволившего в одном кристалле полупроводника размещать сложные вычислительные структуры, содержащие десятки тысяч транзисторов. Изготовление больших интегральных схем (БИС) сопряжено с трудоемкой работой по разработке схем, фотошаблонов и подготовкой производства и служб контроля технологических параметров и характеристик БИС. Снижение себестоимости БИС возможно лишь при максимальной автоматизации этапов, предшествующих их изготовлению, и массовости производства.

Массовое производство БИС предполагает широкий спрос потребителя, а следовательно, возможность ее использования для большого круга решаемых задач. Микропроцессорные БИС (МП БИС) представляют тот класс интегральных схем, который сочетает в себе высокую степень интеграции, обеспечивающую огромные функциональные возможности, с большой универсальностью по применению.

Целями курсового проекта являются:

- изучение методики проектирования микропроцессорных систем от технического задания до рабочих чертежей;

- углубление знаний полученных в теоретических курсах;

- получение навыков внедрения теоретических знаний в практические применения.

Основной задачей курсового проекта является разработка архитектуры, принципиальной схемы и конструкции специализированного микроконтроллера, выполняющего функции, определенные заданием, на базе заданных технических средств.

Исходные данные для проекта

1. Базовый восьмиразрядный микроконтроллер.

2. Оперативные периферийные устройства: индикаторы семисегментные (10 знакомест), клавиатура (16 клавиш), внешние прерывания (3 линии).

3.

Внешние

устройства: входное АЦП (7 каналов, 12 разрядное, ![]() В);

В);

выходное ЦАП

(1 канала, 10 разрядное, ![]() В).

В).

4.

Интерфейс

для связи с дополнительными внешними устройствами ![]() .

.

5. Схема сопряжения с фотоимпульсным датчиком углового положения ФИ.

1 Описание функциональной схемы

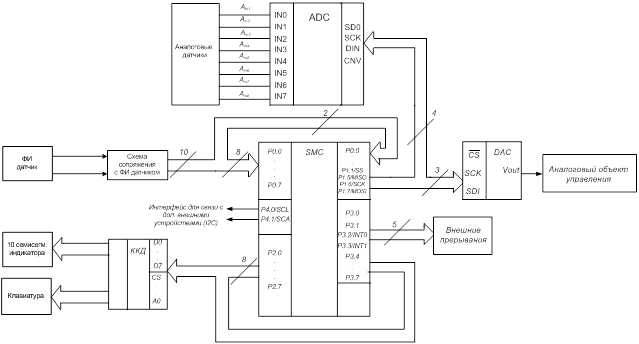

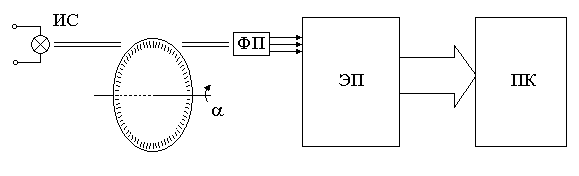

На рисунке 1 представлена функциональная схема микроконтроллера с внешними устройствами.

Рисунок 1 – Схема

электрическая функциональная микроЭВМ

Рисунок 1 – Схема

электрическая функциональная микроЭВМ

Микропроцессорная система включает в себя:

1. Микроконтроллер AT89C5131A-L

2. Контроллер клавиатуры и индикации КР580ВВ79.

3. 1-канальный10-разрядный цифро-аналоговый преобразователь с интерфейсом SPI MAX503

4. 8-канальный 14-разрядный аналого-цифровой преобразователь с интерфейсом SPI AD7949.

5. Схема сопряжения с фотоимпульсным датчиком.

AT89C5131A-L – высокопроизводительная версия 8-разрядного однокристального микроконтроллера 80C51 с флэш-памятью и функциями полноскоростной USB-связи.

Микроконтроллер имеет:

- высокопроизводительное микропроцессорное ядро C51 совместимое со стандартом 8051.

-аппаратно реализованные последовательные интерфейсы I2С, SPI и интерфейс USB

- 34 цифровых входа/выхода

- две линии внешних прерываний.

Микроконтроллер имеет встроенную схему слежения за напряжением питания, сторожевой таймер, тактовый генератор и представляет собой функционально законченную систему на одном кристалле. Все аналоговые и цифровые периферийные модули могут включаться/отключаться и настраиваться программой пользователя.

Контроллер клавиатуры-дисплея (ККД) КР580ВД79 обеспечивает обслуживание клавиатуры (сканирование клавиатуры, и выдача сигнала процессору, при нажатии клавиши) и обслуживание индикаторов (обеспечивается подключение 10 семисегментных индикаторов и регенерацию изображения в динамическом режиме).

В качестве индикатора используется 10 семисегментных индикаторов АЛС348А. Подключается к МК через контроллер клавиатуры/дисплея.

Клавиатура 2×8 (16 клавиш) подключается к МК также через контроллер клавиатуры/дисплея.

Для связи с внешними используется встроенный последовательный интерфейс I2С.

Для обеспечения подключения 12-разрядного ЦАП MCP4921 и 14-разрядного АЦП AD7949 используется встроенный в микроконтроллер последовательный SPI интерфейс.

Для организации трёх клавиш прерывания и прерываний от внешних устройств используется логическая схема расширения прерываний, которая подаёт сигнал прерывания на вход порта Р3.1 и Р3.2 при нажатии одной из клавиш прерывания.

2 Разработка принципиальной схемы

В полную принципиальную схему контроллера, кроме описанного выше блока процессора, входят ЦАП, АЦП, клавиатура, индикаторы.

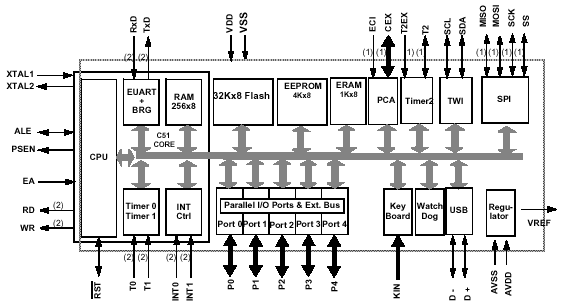

2.1 Описание микроконтроллера

AT89C5131A-L содержит следующие компоненты: 32 кбайт флэш-памяти с поддержкой внутрисистемного программирования через интерфейс USB, 3 кбайт флэш-памяти для загрузочной программы, 1 кбайт ЭСППЗУ для хранения данных, 256 байт ОЗУ, встроенное ОЗУ расширения (ERAM) 1024 байт, встроенная схема контроля питания (сброс при подаче питания/определение снижения напряжения питания), полноскоростной модуль USB, совместимый с требованиями USB1.1 и USB 2.0, 34 линий ввода-вывода общего назначения, байт-ориентированный 2-проводной последовательный интерфейс TWI, последовательный порт SPI (режим ведущий/подчиненный), режимы холостого хода и снижения мощности, расширенный диапазон напряжения питания: 2.7-5.5В.

AT89C5131A-L поддерживает два программно-управляемых режима со сниженной активностью, позволяющие снизить уровень потребления. В режиме холостого хода прекращает работу ЦПУ, а таймеры, последовательные порты и система прерываний продолжают функционировать. В режиме снижения мощности сберегается содержимое ОЗУ и останавливается синхронизация периферийных устройств, а возобновление работы микроконтроллера возможно при возникновении событий USB или внешних прерываний.

Микроконтроллер выпускается по технологии высокоплотной энергонезависимой памяти компании Atmel. Механизм программирования встроенной флэш-памяти позволяет перепрограммировать ее внутрисистемно через последовательный интерфейс SPI с помощью обычного программатора энергонезависимой памяти или с помощью встроенной загрузочной программы, выполняемой ядром AVR. Загрузочная программа может использовать любой интерфейс для загрузки программного кода во флэш-память. За счет разделения флэш-памяти на загрузочный сектор и сектор прикладной программы поддерживается действительная возможность чтения во время записи, когда загрузочный код продолжает исполняться и выполняется обновление сектора прикладной программы.

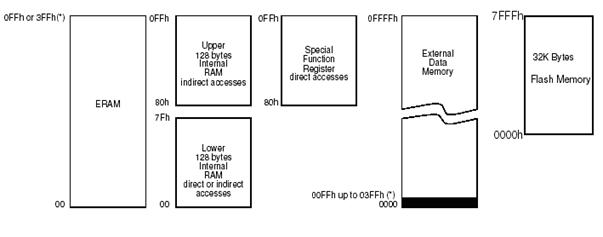

2.2 Организация памяти

В состав памяти входит ОЗУ объемом 256 байт. К младшим 128 байтам можно получить доступ при прямой или косвенной адресации. Старшие 128 байт имеют двойную конфигурацию. В режиме косвенной адресации осуществляется доступ к старшим 128 байтам ОЗУ общего назначения, а в режиме прямой адресации осуществляется доступ к 128 байтам адресного пространства регистров специального назначения (SFR).

При обращении к памяти по адресу выше адреса 7Fh, процессор определяет доступ к старшим 128 байтам RAM данных или к регистрам SFR способом адресации.

Память программ МК состоит из 32 Кбайт Flash-памяти. Эта память может перепрограммироваться внутрисистемно, не требуя при этом специального внешнего напряжения программирования, а используя стандартное напряжение VDD.

Согласно сказанного выше область хранения данных используемых при работе ЦМК удобно расположить в адресах 30h…7Fh, где возможна прямая адресация регистров, в случае нехватки места можно задействовать регистры косвенной адресации 80h…FFh.

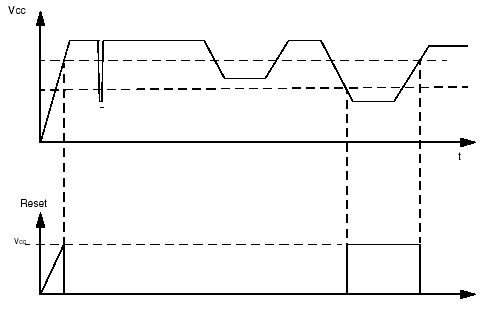

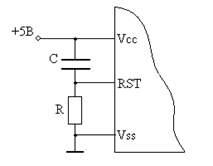

2.3 Формирование сигнала сброс

МК AT89C5131A-L содержат схему слежения за напряжением питания. При включении питания схема контроля питания немедленно осуществляет сброс, которая удерживает МК в состоянии сброса, пока напряжение питания VDD не превысит в процессе включения уровень VRST, в соответствии с временной диаграммой представленной на рисунке. При этом запускается внутренний счетчик для задержки. В течение таймаута схемы слежения за напряжением питания на выводе /RST удерживается низкий логический уровень, что позволяет напряжению питания стабилизироваться.

2.4 ЦАП

MCP4921 – экономичные 12-разрядные цифро-аналоговые преобразователи с возможностью изменения коэффициента передачи выходного буфера и SPI-интерфейсом. Преобразователи обеспечивают высокую точность и малый уровень шумов во всем расширенном диапазоне температур. Данный тип преобразователя может быть использован в телевизионных и радиолокационных системах, системах сбора и обработки данных в реальном масштабе времени, измерительной аппаратуре и др. Конструктивно она выполнена в корпусе типа DIP-8.

Напряжение питания: AVDD=5В, DVDD=5В.

Выходное напряжение: Vout=0…5В;

Разрядность: 12 бит;

Диапазон выходного напряжения соответствует заданным требованиям.

ЦАП сопрягается с МК по интерфейсу SPI в 4-х проводном режим работы. Обращение к ЦАП производится сигналом микроконтроллера с P1.1/SS на вывод выборки микросхемы CS. При этом МК является ведущим устройством, а ЦАП – ведомым.

Сигнал MOSI (master-out, slave-in - «выход ведущего, вход ведомого») является выходом данных ведущего устройства и входом данных ведомых устройств. Он используется для последовательной передачи данных от ведущего к ведомому. Данные передаются старшими значащими разрядами вперед. При работе в ведущем режиме значение сигнала MOSI определяется старшим значащим разрядом сдвигового регистра как в 3-х проводном, так и в 4-х проводном режимах.

Сигнал MISO (master-in, slave-out - «вход ведущего, выход ведомого») является выходом данных ведомого устройства и входом данных ведущего устройства. Он используется для последовательной передачи данных от ведомого к ведущему. Этот сигнал является входом. Данные передаются старшими значащими разрядами вперед. Вывод MISO переводится в высокоимпедансное состояние, когда модуль SPI отключен, а также тогда, когда модуль SPI работает в 4-х проводном режиме как ведомый, который не выбран. Когда модуль SPI работает в 3-х проводном режиме как ведомый, сигнал MISO всегда определяется старшим значащим разрядом сдвигового регистра.

Сигнал SCK (serial clock – «импульсы тактирования последовательного интерфейса») является выходом ведущего устройства и входом ведомых устройств. Он используется для синхронизации обмена данными между ведущим и ведомым устройствами по линиям MOSI и MISO. При этом сигнал SCK игнорируется ведомым SPI, когда ведомый не выбран (SS = 1).

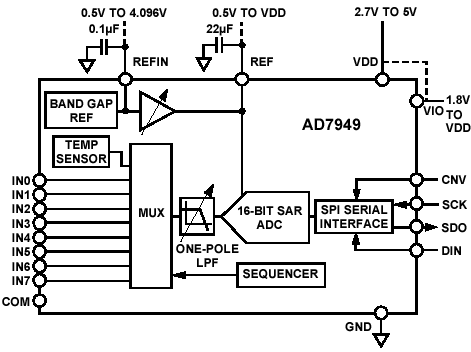

2.5 АЦП

По заданию устройство должно считывать информацию

с восьми аналоговых каналов, имеющих диапазон входного напряжения ![]() и преобразовывать

входной аналоговый сигнал в 14-ти разрядный цифровой код на выходе.

и преобразовывать

входной аналоговый сигнал в 14-ти разрядный цифровой код на выходе.

Для этого выбираем АЦП AD7949 фирмы Analog Devices. Данный АЦП имеет 8 аналоговых входа и диапазон входного напряжения от 0 B до 5 В, поэтому необходимо вводить дополнительные внешние элементы для преобразования входного напряжения. Снижение уровня сигнала осуществляется на микросхемах DA1 – DA4 AD-8513, имеющих в своем составе по четыре операционных усилителя. На двух усилителях происходит снижение напряжения, при этом они включены по инвертирующей схеме, на двух других осуществляется инверсия сигнала. Условное графическое обозначение микросхемы операционного усилителя представлено на рисунке 14.

Рисунок – Функциональная блок схема АЦП

АЦП типа AD7949 предназначена для применения в электронной аппаратуре в составе блоков аналогового ввода. Микросхема выполняет функцию 8-канального 14-разрядного аналого-цифрового преобразования однополярного или биполярного входного сигнала с представлением результатов преобразования в последовательном двоичном коде.

Для организации обмена информацией используется также SPI интерфейс. Обращение к АЦП производится сигналом микроконтроллера с P1.1/SS на вывод выборки микросхемы CNV. При этом МК является ведущим устройством, а АЦП – ведомым.

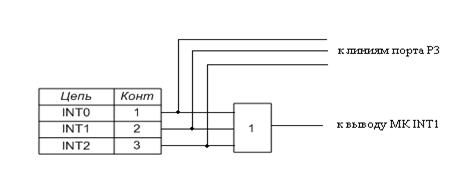

2.6 Организация прерываний

Прерывания осуществляются от 3 клавиш и от контроллера клавиатуры/дисплея. Сигнал прерывания, приходящий от ККД, поступает на вход Р3.2/INT0 МК.

Поскольку количество источников прерываний больше линий внешних прерываний микроконтроллера, то необходимо использовать дополнительную логическую схему «ИЛИ». При осуществлении хотя бы одного прерывания сигнал с элемента «ИЛИ» приходит на линию Р3.3/INT1 МК. При этом на одну из линий порта Р3 (P3.0, P3.1, P3.4) подается логическая 1. Таким образом, проанализировав программно состояние линий Р3.0, Р3.1 и Р3.4 можно в зависимости от номера нажатой клавиши передать управление подпрограмме обработки данного прерывания.

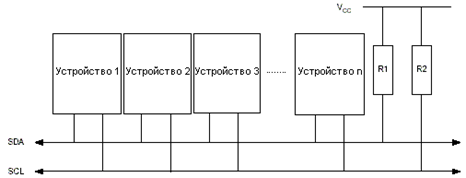

2.7 Последовательный интерфейс I2C

В данном разделе приводится описание двухпроводного последовательного I2C -интерфейса, так как он используется для обмена информацией между микроконтроллером внешними периферийными устройствами. В данном микроконтроллере данный интерфейс именуется как интерфейс TWI. Протокол TWI позволяет связываться с устройствами через одну двухпроводную двунаправленную шину, где одна линия - линия синхронизации SCL и одна - линия данных SDA.

В качестве внешних аппаратных компонентов, которые требуются для реализации шины, необходимы только подтягивающий к плюсу питания резистор на каждой линии шины. Все устройства, которые подключены к шине, имеют свой индивидуальный адрес. Внешнее подключение устройств к шине TWI изображено на рисунке….

Подключение устройств к шине TWI

Протокол передачи данных по шине разработан таким образом, чтобы гарантировать надежный качественный прием/передачу данных. При передаче данных одно устройство является “Ведущим”, которое инициирует передачу данных и формирует сигналы синхронизации. Другое устройство “Ведомое”, которое может начать передачу данных только по команде ведущего шины.

Каждое устройство на шине имеет уникальный адрес. Когда ведущий инициирует передачу данных, то сначала передается адрес устройства, к которому выполняется обращение. Остальные устройства проверяют переданный ведущим адрес. В составе байта адреса устройства входит бит направления передачи данных (выполняется чтение из ведомого или запись). Ведомый и ведущий шины всегда находятся в противоположном режиме работы, что можно представить в виде двух состояний: ведущий передатчик – ведомый приемник; ведомый передатчик – ведущий приемник. В обоих случаях ведущий формирует тактовый сигнал.

Вывод тактового сигнала SCL и данных SDA должны иметь выход с открытым коллектором, чтобы выполнять требования “монтажного И” на шине. Число устройств, которые могут быть подключены к шине, ограничивается только максимальной емкостью шины (400 пФ).

3 Описание работы контроллера клавиатуры/дисплея КР580ВД79

микроконтроллер разработка схема

Микросхема КР580ВД79, именуемая для краткости ККД (контроллер клавиатуры/дисплея), представляет собой универсальное программируемое устройство сопряжения с клавиатурой и дисплеем на основе семисегментных светодиодных индикаторов (ССИ).

Он состоит из двух основных функционально разделимых частей: клавиатурной и дисплейной. Клавиатурная часть предназначена для сопряжения с клавиатурой печатающих устройств и с произвольными наборами переключателей. Дисплейная часть ПККИ позволяет отображать информацию с помощью индикаторов различных типов (дисплеев). В нашем случае используется десять семисегментных индикаторов, которые используются в качестве алфавитно-цифрового дисплея.

Клавиатурная часть обеспечивает работу с клавиатурой размером 8x8 + 2 клавиши или с матрицей 8x8 датчиков. Обеспечиваются различные дисциплины распознавания нажатых клавиш, антидребезговый контроль. Имеется память кодов нажатых клавиш на 8 байт, организованная в виде очереди FIFO. При занесении в эту память более 8 кодов устанавливается признак переполнения. Нажатие клавиши возбуждает линию прерывания, которая может опознаваться в МК.

Дисплейная часть обеспечивает работу с дисплеем на семисегментных индикаторах (их может быть до 32 шт.). Имеется ОЗУ дисплея на 16 байт, организованное в виде двух массивов 16х4 бита. Память дисплея может быть загружена из МК и прочитана им. И в том, и в другом случае возможно автоинкрементирование адреса ОЗУ дисплея. Таким образом, ККД освобождает МК от задач постоянного сканирования клавиатуры и поддержания изображения на дисплее.

Назначение входных, выходных и управляющих сигналов ПККИ приведено в таблице 3.

Таблица 3

| Обозначение вывода | Назначение вывода |

| RL0-RL7 | Входы линий возврата, служащие для подачи сигналов от датчиков через контакты клавиш или ключа |

| SHIFT | Вход сигнала сдвига, используемого для сканирования клавиатуры |

| CNTL/STB | Вход сигнала управления для режима сканирования клавиатуры или стробирующего сигнала для режима ввода по стробу |

| RD | Вход сигнала чтения L-уровня, разрешающего передачу информации из ПККИ в канал данных микропроцессора |

| WR | Вход сигнала записи L-уровня, разрешающего передачу информации из канала данных микропроцессора в ПККИ |

| A0 | Вход для управления записью/чтением данных или команд; при сигнале Н-уровня происходит запись команды или чтения состояния ПККИ, при сигнале L-уровня — запись или чтение данных |

| CS | Выбора микросхемы; L — уровень сигнала разрешает работу схемы |

| CLK | Вход сигнала синхронизации микросхемы |

| RESET | Линия сброса ПККИ в начальное состояние |

| DB0 – DB7 | Двунаправленная шина данных |

| OA0 – OA3 | Выходы канала А (старшая тетрада) |

| OB0 – OB3 | Выходы канала В (младшая тетрада) |

| BD | Выход сигнала гашения отображения L-уровня |

| SL0 – SL3 | Выходы сигналов сканирования клавиш клавиатуры |

| IRQ | Выход сигнала прерывания |

Управление ККД с помощью сигналов на внешних выводах.

Управляющие

слова (УС) загружаются в регистры управления ККД при ![]() . Загружая определенные УС, можно

настроить ККД на работу в требуемом режиме и предписать выполнение некоторой

операции.

. Загружая определенные УС, можно

настроить ККД на работу в требуемом режиме и предписать выполнение некоторой

операции.

Операции, выполняемые в ККД, определяются не только управляющим словом, но и комбинацией управляющих сигналов на его входах:

Направление и вид операций обмена между микропроцессором и ПККИ представлены в таблице 4.

Таблица 4

| Сигналы управления | Вид операции обмена | |||

| CS | A0 | RD | WR | |

| 1 | X | X | X | ПККИ не выбран |

| 0 | X | 1 | 1 | ПККИ не выбран |

| 0 | 0 | 0 | 1 | Чтение данных из памяти клавиатуры или дисплея |

| 0 | 0 | 1 | 0 | Передача команды с ШД в ПККИ |

| 0 | 1 | 0 | 1 | Чтение байта состояния ПККИ |

| 0 | 1 | 1 | 0 | Загрузка управляющего слова в ПККИ |

УС инициализации клавиатуры и дисплея (УС0):

0.0.0.D.D.KK.S.

Здесь DD кодирует режим работы дисплея, КК - режим работы клавиатуры, S - режим сканирования в соответствии со следующими правилами:

DD:00Дисплей на 8 символов с вводом слева

01Дисплей на 16 символов с вводом слева

10Дисплей на 8 символов с вводом справа

11Дисплей на 16 символов с вводом справа

Описание режимов правого и левого вводов приводится ниже. Если сканирование идет в режиме дешифратора, то дисплей не может быть больше, чем на четыре символа (так как линии SL общие).

КК: 00 Клавиатура в режиме одиночного нажатия клавиш

01 Клавиатура в режиме N-клавишного нажатия

10 Сканирование матрицы датчиков

11 Режим стробируемого ввода

S:0Сканирование в режиме 4-битного двоичного счетчика

1Сканирование в режиме инверсного дешифратора на четыре выхода.

После сброса ККД оказывается в режиме, соответствующем УС0-00001000. При сканировании в режиме счетчика цикл опроса клавиатуры укладывается в восемь состояний счетчика от "0000" до "0111" и oт "1000" до "1111". Таким образом, в этом режиме опрос клавиатуры происходит дважды в каждом цикле полного пересчета счетчика SLO—SL3, т.е. для сканирования клавиатуры используются только три младшие линии SLO-SL2.

УС инициализации опорной частоты (УС1): О.О.1.Р.Р.Р.Р.Р. Здесь РРРРР устанавливает коэффициент деления частоты внешнего синхросигнала CLK для получения внутреннего опорного сигнала с частотой не более 100 кГц. После сброса устанавливается максимальный коэффициент РРРРР, равный 11111. При частоте внутреннего опорного сигнала 100 кГц один полный цикл сканирования занимает приблизительно 10,2 мс.

УС чтения памяти клавиатуры/датчиков (УС2): О.1.0.I.Х.А.А.А. УС2 должно предшествовать чтению данных из памяти клавиатуры. Здесь I есть признак автоинкрементной адресации; ААА устанавливает адрес байта памяти, который должен быть считан. Если бит I установлен, то последующие команды чтения данных будут вызывать автоматическое увеличение адреса. Таким образом, если необходимо прочитать всю память клавиатуры, то это можно сделать, загрузив УС2 с битом I = 1 и затем 8 раз считать данные из ККД.

УС чтения памяти дисплея (УСЗ): 0.1.1.I.A.AA.A. УСЗ должно предшествовать чтению данных из памяти дисплея. Здесь I есть признак автоинкрементной адресации: АААА — номер позиции дисплея, которая должна быть считана. Если I = 1, то адрес будет инкрементироваться после каждого чтения.

УС записи в память дисплея (УС4): 1.0.0.1.А.А.А.А. Кодирование аналогично УСЗ. Поле АААА определяет адрес байта в ОЗУ дисплея.

УС запрета записи в память дисплея и бланкирования дисплея (УС5): 1.0.1.X.IWA.IWB.BLA.BLB. Здесь IW - указатель запрета записи (тетрады А и В), BL - указатель бланкирования (очистки) (тетрады А или В). Если дисплей используется как двойной 4-позиционный, то удобно маскировать одну из тетрад, чтобы работа процессора с одной тетрадой не отражалась на другой. Эту возможность дает указатель IW. Указатель BL используется для бланкирования дисплея; если он установлен. То на выходах А и/или В устанавливается специальный бланкирующий код (см. УС6). Содержимое памяти дисплея при этом не изменяется, Если дисплей используется как единый 8-позиционный, то необходимо устанавливать оба указателя.

УС сброса памяти дисплея (УС6): 1.1.0.CD.BC.BC.CF.CA. УС6 служит для: выбора кода бланкирования (ВС), сброса байта состояния (CF) и сброса памяти дисплея (CD). Биты ВС позволяют выбрать один из трех возможных бланкирующих кодов.

После общего сброса контроллера бланкирующий код устанавливается равным ООН.

Процедура сброса памяти дисплея осуществляется путем заполнения кодами бланкирования. Процедура инициируется при установке бита CD и продолжается примерно 160 мкс. В это время память дисплея недоступна, на что указывает старший бит байта состояния контроллера.

Бит CF, будучи установлен, сбрасывает байт состояния, сигнал прерывания и устанавливает указатель памяти матрицы датчиков на строку 0. Управляющий бит СА работает как биты CD и CF в совокупности, а также сбрасывает схему внутренней синхронизации.

УС сброса прерывания/установки режима ошибки (УС7): U.1.E.X.X.XX В состоянии матрицы датчиков УС7 сбрасывает линию прерывания и разрешает дальнейшую запись в память клавиатуры (матрицы датчиков). В режиме N-клавишного нажатия, если установлен бит Е, контроллер переходит в режим ошибки.

Режим одиночного нажатия клавиш. Дисциплина опознания нажатых клавиш в этом режиме такова: если обнаружено нажатие одной клавиши, то в течение следующих двух циклов сканирования клавиатуры будет производиться проверка нажатия других клавиш. Если таких клавиш не будет, то нажатая клавиша признается единственной и код ее записывается в память клавиатуры. Если в течение этих двух циклов будет обнаружено нажатие еще одной клавиши, то в память клавиатуры не заносится код ни одной клавиши до тех пор, пока не будут освобождены все клавиши, кроме одной. После того как все, кроме одной, клавиши будут освобождены и не будут нажаты новые в течение двух циклов, код этой клавиши будет занесен в память клавиатуры. Код клавиши заносится в память клавиатуры только один раз на каждое нажатие.

Режим N-клавишного нажатия. В этом режиме нажатие каждой клавиши фиксируется независимо от состояния остальных клавиш. Когда клавиша нажата, пропускаются два цикла опроса клавиатуры, а затем проверяется, осталась ли данная клавиша нажатой. Если да, то ее код заносится в память. При одновременном нажатии распознавание клавиш производится в порядке их опроса в цикле сканирования клавиатуры. Опознание всех клавиш ведется независимо. На каждое нажатие код клавиши вводится только один раз.

Специальный режим ошибки при сканировании клавиатуры. Для режима сканирования клавиатуры с N-клавишным нажатием с помощью УС7 можно запрограммировать специальный режим ошибки. Если в течение одного цикла сканирования будут нажаты две клавиши, это трактуется как совместное нажатие и устанавливается флаг ошибки в байте состояния. Этот флаг запрещает дальнейшую запись в память клавиатуры и устанавливает линию прерывания (если она не была установлена). Флаг ошибки можно сбросить с помощью УС6, установив в нем CF= 1.

Режим матрицы датчиков. В этом режиме "антидребезговая" логика не работает. Состояние датчиков непосредственно записывается в память матрицы датчиков (память клавиатуры). Хотя антидребезговый контроль и не обеспечивается, МК может иметь информацию о том, как долго датчик находится в единичном или нулевом состоянии (у датчика подразумеваются только два состояния). Линия прерывания устанавливается в единицу, если в конце цикла сканирования матрицы хотя бы один из датчиков изменил свое состояние, и сбрасывается при первой же операции чтения, если не был установлен указатель автоинкрементирования.

Форматы данных. В режиме клавиатуры байт, записываемый в память клавиатуры, отражает положение клавиши на клавиатуре, а также состояние входов CNTL и SHIFT. Формат данных в этом режиме CNTL.SHIFT.SL2.SL1.SL0.R2.R1.RO.

Здесь SL2-SLO - двоичный код строки, в которой находится клавиша, R2-RO - двоичный код колонки, в которой находится клавиша (номер линии RL, на которую поступил нулевой сигнал).

В состоянии матрицы датчиков данные, приходящие на линии RL7—RLO, непосредственно вводятся в память клавиатуры. Таким образом, каждое изменение в датчиках в течение одного цикла будет отражено в памяти. Состояния SHIFT и CNTL игнорируются.

Формат данных в режиме стробируемого ввода; RL7.RL6.RL5.RL4, RL3.RL2.RL1.RLO. В этом режиме данные также вводятся в память по линиям RL7-RL0, но при этом ввод стробируется линией CNTL/STB. Данные заносятся в память по фронту сигнала CNTL/STB.

Следует помнить, что цикл сканирования клавиатуры постоянен, не зависит от размера дисплея и соответствует максимальной конфигурации клавиатуры 8x8 при сканировании в режиме счетчика и 4х8 при сканировании в режиме дешифратора.

Режимы работы дисплея

Ввод слева. Это самый простой формат ввода. При нем каждой позиции на дисплее однозначно соответствует байт в памяти дисплея. Нулевой адрес памяти дисплея соответствует самой левой нулевой позиции дисплея, адрес 15 (7 для 8-позиционного дисплея) соответствует самой правой позиции дисплея. При переходе за 16 (8) позиций следующие символы будут опять вводиться слева с нулевой позиции, т.е. 17-й (9) символ займет крайнюю левую позицию.

Ввод справа. Этот способ ввода используется в калькуляторах. Первый вводимый символ заносится в крайнюю правую позицию. Следующие символы также заносятся в крайнюю правую позицию, но после того, как все символы на дисплее сдвинутся на одну позицию влево. Самый левый символ при этом теряется. Заметим, что здесь номера позиций на дисплее уже не соответствуют адресам памяти дисплея. Адрес памяти дисплея в этом случае соответствует порядковому номеру нажатой клавиши. Указание позиции, в которую должен быть введен символ при автоинкрементируемом вводе (см. далее), может иметь непредсказуемый результат.

Автоинкрементирование. В состоянии ввода слева это означает, что следующий символ, поступающий из МК, будет размещен по адресу, на единицу большему, чем предыдущий. При отсутствии автоинкремента ввод будет произведен в ту же самую позицию. Использование автоинкремента при вводе слева не порождает непредсказуемых эффектов, даже если после ввода нескольких символов нужно ввести очередной символ не в следующую, а в произвольную позицию. Это обусловлено тем, что позиция на дисплее при вводе слева однозначно соответствует адресу памяти дисплея. При вводе справа с автоинкрементированием попытка ввести символ в фиксированную позицию будет иметь непредсказуемый результат.

Формат дисплея. Если используется 8-позиционный дисплей, то время цикла сканирования дисплея в 2 раза меньше, чем для 16-позиционного дисплея. При внутренней частоте 100 кГц это время составляет 1 и 10,2 мс соответственно.

Байт состояния памяти клавиатуры/датчиков

Байт состояния используется в режиме клавиатуры и стробируемого ввода для отображения числа введенных символов и индикации ошибки. Возможны два вида ошибок: переполнение и пеpeoпустошение. Флаг переполнения устанавливается, когда делается попытка записи в заполненную память клавиатуры. Флаг переопустошения устанавливается, если была попытка считать из пустой памяти клавиатуры. Байт состояния имеет также бит DU, показывающий, что дисплей недоступен из-за того, что завершена очистка памяти дисплея. В специальном режиме ошибки бит S/E является флагом ошибки и указывает на множественное нажатие клавиш. В режиме матрицы датчиков этот бит показывает, что имеется хотя бы один "замкнутый" (нулевой) датчик.

Формат байта состояния памяти клавиатуры/датчиков: DU.S/E.O.U.F.N.N.N

DU - дисплей недоступен;

S/E - датчик "замкнут"/ошибка многократного нажатия;

О - ошибка переполнения;

U - ошибка переопустошения;

F — память клавиатуры заполнена;

NNN — количество символов в памяти клавиатуры.

4 Схема сопряжения микроконтроллера с фотоимпульсным датчиком

Основным элементом ФИД является прозрачный диск с нанесенными на него рисками, количество которых достигается нескольких тысяч. При повороте диска, луч света, излучаемый источником ИС, модулируется рисками и воспринимается фотоприемниками ФП. Электрические сигналы от ФП преобразуются электронным преобразователем ЭП в систему электрических сигналов, которые подаются на микроконтроллер.

Схема фотоимпульсного датчика скорости

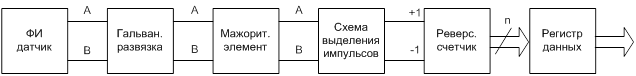

В качестве электронного преобразователя рассматривается следующая схема сопряжения ФИД с цифровой системой.

Структурная схема

сопряжения ФИ датчика

Структурная схема

сопряжения ФИ датчика

с цифровой системой управления

4.1 Гальваническая развязка

В качестве гальванической развязки возможно применение

- трансформаторы

- оптопары

Используется оптопара, выполненная на микросхеме… Каждая оптопара ставится на каждый канал фотоимпульсного датчика.

4.2 Мажоритарный элемент

Имеет нечетное число входов и один выход. Сигнал на выходе элемента получает то значение, которое имеется не большинстве его входов. Если необходимо создать мажоритарный элемент на какое-либо количество входов, то необходимо суммировать все сигнал от элементов «И», на входы которых подаются все комбинации входных сигналов от большинства.

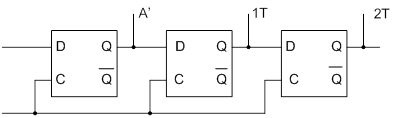

Поскольку мажоритарный элемент используется для выявления и устранения кратковременных импульсных помех, то сначала необходимо выполнить сдвиг информационного сигнала на некоторое количество тактов.

Сдвиг информационного сигнала можно выполнить на D-триггерах (в данном проекте используется 3 D-триггера для одного канала сигналов).

Схема сдвига сигнала

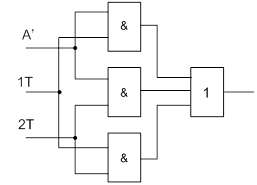

Для данной схемы возможно всего 3 комбинации:

| A’ | 1T | 2T |

|

1 1 0 |

1 0 1 |

0 1 1 |

Следовательно, необходимо 3 элемента «И» и одни «ИЛИ». Схема мажоритарного элемента будет иметь вид (см. рисунок 12).

4.3 Схема выделения импульсов

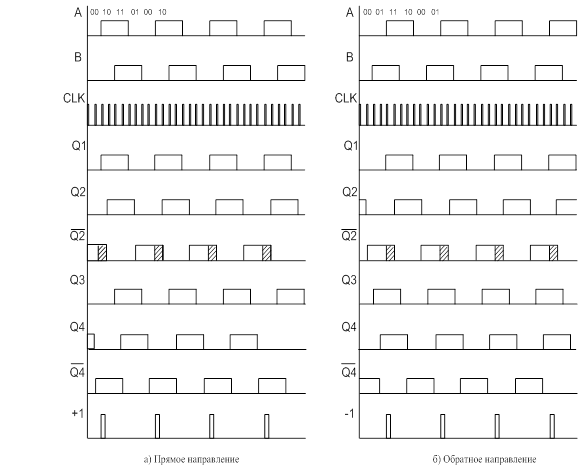

Широко распространена схема выделения импульсов, собранная на мультиплексорах. Для определения входных данных мультиплексора составляются диаграммы входных импульсов (см. рисунок 10). Поскольку задан датчик без умножения, то будем считать, что выходной импульс формируется по фронту сигнала А.

Диаграмма этих сигналов при вращении вправо и влево показана на рисунке11. При этом необходимо обеспечить, чтобы при движении вправо при каждом переходе входного сигнала происходит прибавление 1http://www.unilib.neva.ru/dl/532/k9-2-1.gif в счетчике, а при движении влево – вычитание 1. Таким образом, в счетчике ПК формируется код угла поворота Na или его приращения.

Поскольку задан датчик без умножения, то разрядность счетчиков равна 10.

Используются три микросхемы 4-разрядных реверсивных двоичных счетчиков К555ИЕ7, соединенных по схеме увеличения разрядности.

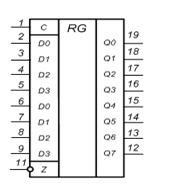

Для передачи данных в микроконтроллер используются 2 микросхемы буферных регистров К555ИР33

Запись данных в регистр производится с приходом такта на вход С. Для чтения информации с МК на вход Z подается сигнал H-уровня. При этом выходы регистра переходят из высокоимпедансном состояния в обычное.

5 Расчет потребляемого тока от источника питания

Токи, потребляемые элементами, входящими в состав микроконтроллера для обработки дискретных сигналов, приведены в таблице 5.

Таблица 5

| Микросхема | Наименование элемента | Количество элементов | Потребляемый ток, мА |

| DD1 | AT89C5131A-L | 1 | 25 |

| DD2 | MCP4921 | 1 | 24 |

| DD3 | AD7949 | 1 | 50 |

| DD4 | КР580ВД79 | 1 | 60 |

| DD5 | К555ИД3 | 1 | 35 |

| DD6-DD8 | К555ИЕ7 | 3 | 3*20 |

| DD9-DD10 | К555ИР33 | 2 | 2*20 |

| DD11 | К555ТМ8 | 1 | 15 |

| DD12 | К555ТМ9 | 1 | 18 |

| DD13 | К555КП2 | 1 | 10 |

| DD14 | К555ЛЛ1 | 1 | 10 |

| DD15-DD16 | К555ЛИ1 | 2 | 11.5*2 |

| HG1-HG9 | АЛС348А | 10 | 8*10 |

Суммарный

ток, потребляемый элементами микроконтроллера от источников питания, составляет

![]() 395мА.

395мА.

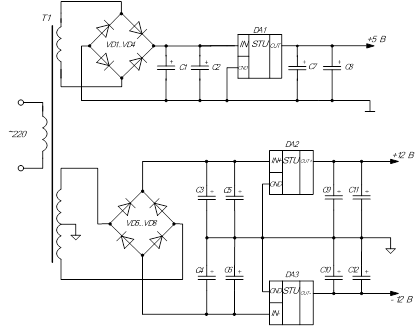

РАСЧЕТ БЛОКА ПИТАНИЯ

Блок питания должен быть хорошо отфильтрован и стабилизирован /1/. Поэтому применяется схема двухполупериодного выпрямления со стабилизатором на интегральных микросхемах (рисунок 4.1.). Необходимо получить выходное напряжение для питания микросхем +5В, +12В и –12В. При этом двух полярное напряжение необходимо для питания операционных усилителей, а остальные микросхема работают при напряжении +5В.

Схема блока питания приведена на рисунке 21.

Схема блока питания

Понижающий трансформатор Т1 необходим для гальванической развязки питания цифровой и аналоговой частей. В качестве схемы выпрямления используется диодный мост КЦ405Е (100В, 1А). Напряжение снимается с микросхем стабилизаторов: MC78L05 с выходным напряжением Uвых=5 В; MC78L12 с выходным напряжением Uвых=12 В; MC79L12 с выходным напряжением Uвых=-12 В. Входные конденсаторы C2, C5, C6 имеют емкость 0.33 мкФ и предназначены для сглаживания входного напряжения, поступающего на стабилизатор. Выходные конденсаторы C7, C9, C10 емкостью 0.1 мкФ не являются необходимыми, но существенно улучшают характер переходного процесса при включении электропитания. Остальные конденсаторы – сглаживающие: C1, C3, C4 – К50-35 1000 мкФ; C8, C11, C12 – К50-35 100 мкФ.

6 Программная часть

Блок-схема программы вывода информации на индикацию представлена на рис. 21.

Блок-схема программы

HG:

CLR P0.4;выбор кристалла

SETB P0.3;направление передачи МК à ККД

CLR P0.7;

SETB P0.6;запись в ККД

MOV P2,00000000B;инициализация клавиатуры и индикаторов

MOV P2,00111111B;инициализация опорной частоты

CLR P0.3;начало записи данных в память дисплея

MOV R0,10010000B;начальный адрес памяти дисплея в ККД

MOV R1,07H;счётчик

MOV R2,50H;начальный адрес массива данных на индикацию в МК

M:

MOV P2,R0;выбор ячейки в памяти ККД

MOV P2,@R2;запись в неё очередного значения из массива

INC R0

INC R2

DEC R1

JNC M;переход если нет переноса

SETB P0.7;

CLR P0.6;данные записаны

RET