Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Курсовая работа: Розробка технічних засобів обміну інформацією для банківської системи з визначенням та виправленням помилок

Курсовая работа: Розробка технічних засобів обміну інформацією для банківської системи з визначенням та виправленням помилок

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут автоматики, електроніки та комп’ютерних систем управління

Факультет автоматики та комп’ютерних систем управління

Кафедра АІВТ

РОЗРОБКА ТЕХНІЧНИХ ЗАСОБІВ ОБМІНУ ІНФОРМАЦІЄЮ ДЛЯ БАНКІВСЬКОЇ СИСТЕМИ З ВИЗНАЧЕННЯМ ТА ВИПРАВЛЕННЯМ ПОМИЛОК

Пояснювальна записка

з дисципліни: “Основи техніки збирання, оброблювання та передавання інформації ”

до курсового проекту за спеціальністю

“Системи автоматики та управління“

08-02.ОТЗОПІ.059. 00.000 ПЗ

Вінниця 2009

Завдання № 59

на курсовий проект

з курсу “Основи техніки збирання, оброблювання та передавання інформації”

Розробити технічні засоби обміну інформацією для банківської системи з визначенням та виправленням помилок.

Вихідні дані: Режим роботи – напівдуплексний.

Режим передавання/приймання – асинхронний.

Тип коду – згортковий.

Кількість помилок, що виникають у кодовій комбінації – 1.

Швидкість передавання – 9600 біт/с.

Вид сигналу – біполярний.

Амплітуда сигналу – 5 В.

1. Охарактеризувати завданий режим зв’язку з урахуванням специфики системи.

2. Описати принципи утворення коду.

3. Розробити структурну схему контролера з урахуванням вибраного формату обміну даними.

4. Визначити кількість контрольних символів і сформувати таблицю кодування-декодування.

5. Розробити функціональну схему.

6. Розрахувати необхідні параметри модулів.

7. Обґрунтувати вибір елементної бази.

8. Розробити принципову схему.

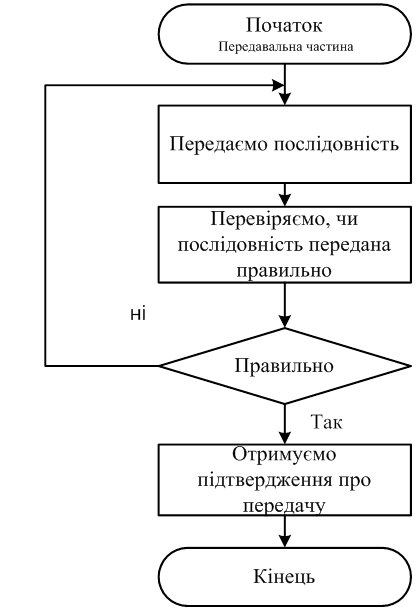

9. Розробити алгоритмічне забезпечення та схеми основних визначених програмних модулів (кодування, декодування, обміну інформацією тощо) з обгрунтуванням вибору режиму обміну інформацією (програмного опитування, переривань, прямого доступу до пам’яті).

10. Розробити відповідне програмне забезпечення з обґрунтуванням вибору мови програмування.

Обговорено і затверджено на засіданні кафедри АІВТ «29» серпня 2009 р.

Протокол № 1. Дата видачі «09» вересня 2009 р.

Зміст

Вступ

1 Принципи утворення згорткових кодів

2 Режими зв’язку

2.1 Асинхронний режим

2.2 Напівдуплексний режим

3 Вибір елементної бази

3.1 Універсальний синхронно-асинхронний приймач-передавач

3.2 Мікроконтролер КМ1816ВЕ51

4 Розробка структурної схеми

5 Розробка функціональної схеми

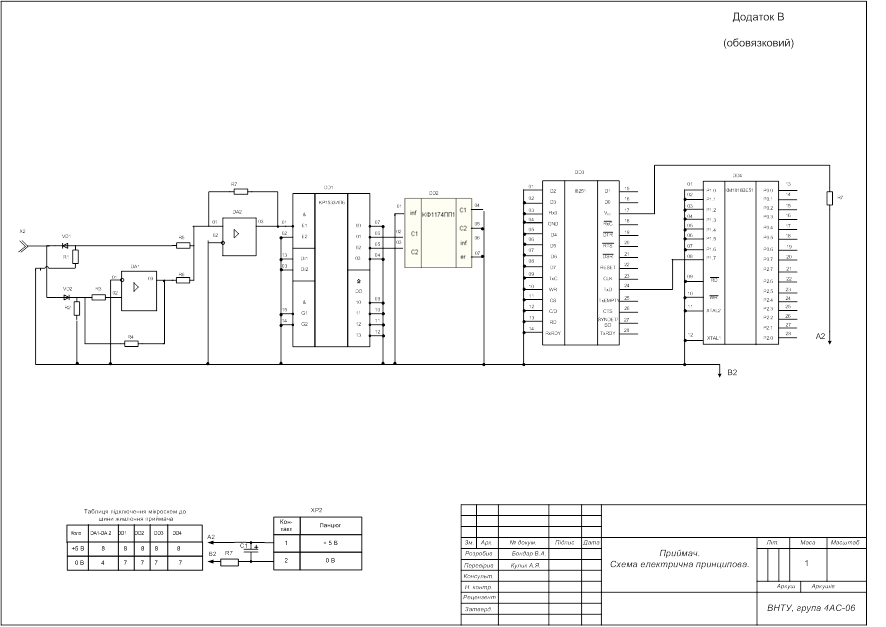

6 Розробка принципової схеми

7 Вибір та обґрунтування мови програмування

Висновки

Література

Додатки

Додаток А (обов'язковий) Технічне завдання

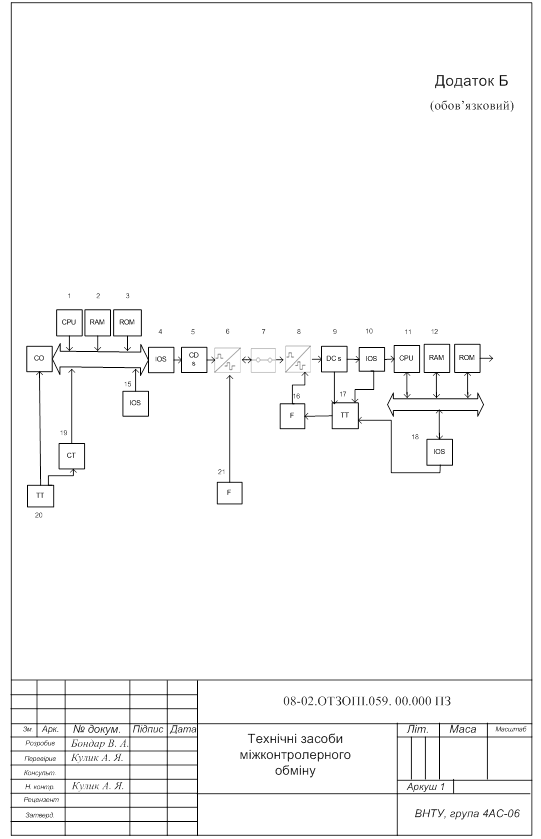

Додаток Б (обов'язковий) Схема електрична структурна

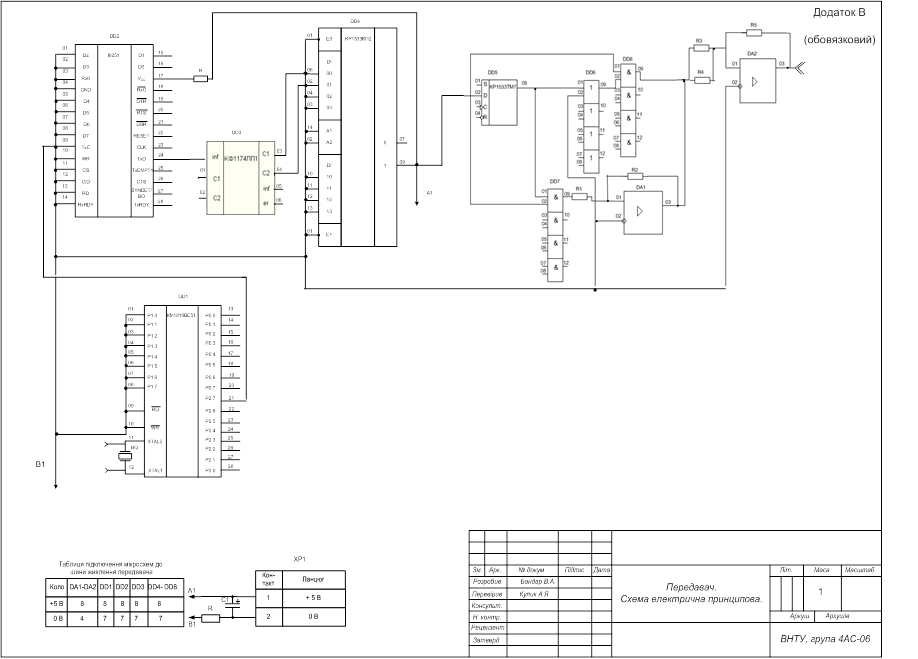

Додаток В (обов'язковий) Схема електрична принципова

Додаток Г (довідниковий) Перелік елементів

Додаток Д (обов'язковий) Схема програми

Додаток Е (обов'язковий) Лістинг програми

Анотація

В курсовому проекті розроблено технічні засоби міжконтролерного обміну інформацією з визначенням та виправленням помилок, описано принципи утворення коду, розроблено структурну схему контролера, функціональну та принципову схеми. В курсовому проекті обґрунтовано вибір елементної бази та розроблено програмне забезпечення з обґрунтуванням мови програмування.

Вcтуп

Стрімкий розвиток банків та банківських систем спонукав до розроблювання нових засобів зв’язку і впровадження нових методів передавання інформації між банками, філіями, відділеннями, банкоматами. В існуючих у теперішній час інформаційно-обчислювальних мережах широко використовуються програмні методи оброблювання та спеціалізовані зв’язкові процесори.

Перша спроба ввести науково обгрунтовану міру інформації була зроблена в 1927 році Р. Хартлі (Англія). Він запропонував та обгрунтував кількісну міру, яка дозволяє порівнювати спроможність різних систем передавати інформацію [1]. Ця міра підходить і для систем зберігання інформації, тому вона є відправною точкою для створення теорії інформації.

Природною вимогою, що пред’являється до інформаційної міри є вимога адитивності, тобто кількість інформації, що може бути збережена у двох однакових комірках повинна бути удвічі більшою за ту, що зберігається в одній з них.

Якщо одна

комірка для зберігання інформації має m можливих станів, то дві таких комірки

будуть мати ![]() можливих

станів, а n однакових комірок -

можливих

станів, а n однакових комірок - ![]() можливих станів. Це саме

стосується і кількості можливих повідомлень. Якщо символ може прийняти значення

«0» або «1», то з одного символу можуть бути одержані 2 повідомлення, з двох

символів - 4, з трьох - 8 тощо [2].

можливих станів. Це саме

стосується і кількості можливих повідомлень. Якщо символ може прийняти значення

«0» або «1», то з одного символу можуть бути одержані 2 повідомлення, з двох

символів - 4, з трьох - 8 тощо [2].

Інформація, що зберігається на носію, може зчитуватись, передаватись, знов записуватись, тобто вона може багаторазово переходити з однієї форми існування до іншої.

Основна проблема - передавання інформації з найменшими втратами.

1 Принципи утворення згорткового коду

Згорткові коди відносяться до безперервних рекурентних кодів. Кодове слово є згорткою відгуку лінійної системи (кодера) на вхідну інформаційну послідовність. Тому згорткові коди є лінійними, для яких сума будь-яких кодових слів також є кодовою послідовністю.

Розглянемо згортковий код з швидкостями вигляду ![]() , де

, де ![]() - деяке натуральне

число.Послідовність символів такого згорткового коду складається з елементарних

блоків завдовжки

- деяке натуральне

число.Послідовність символів такого згорткового коду складається з елементарних

блоків завдовжки ![]() , причому

, причому ![]() символів поточного блоку (що

займають реальний час, що відповідає одному інформаційному біту) є лінійною

комбінацією поточного інформаційного біта і m попередніх. Значення m визначає пам'ять коду, а

параметр m + 1 називається довжиною кодового обмеження. Якщо один (наприклад,

перший) з

символів поточного блоку (що

займають реальний час, що відповідає одному інформаційному біту) є лінійною

комбінацією поточного інформаційного біта і m попередніх. Значення m визначає пам'ять коду, а

параметр m + 1 називається довжиною кодового обмеження. Якщо один (наприклад,

перший) з ![]() символів

поточного блоку повторює поточний інформаційний біт, код називається

систематичним.

символів

поточного блоку повторює поточний інформаційний біт, код називається

систематичним.

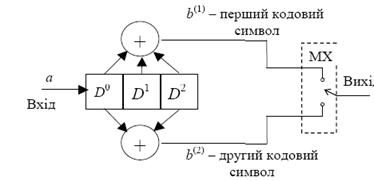

Кодер загорткового коду містить тактований регістр памяті для збереження визначеного числа інформаційних символів і перетворювач вхідної інформаційної послідовності у вихідну кодову послідовність. Структурна схема кодера ЗК (7.5) зображена на рисунку 1.3.

Рис.1.3 – Структурна схема кодера

Послідовність кодування детально розписана в таблиці 1.

Таблиця 1 - Процес кодування послідовності інформаційних бітів 01101000

Способи задання згорткових кодів багато в чому збігаються з

використовуваними для лінійних блокових. Одним з основних є опис згорткового

коду набором ![]() многочленів. Кожен многочлен

встановлює закон формування одного з

многочленів. Кожен многочлен

встановлює закон формування одного з ![]() символів в групі і має міру, що

не перевищує m.

Ненульові коефіцієнти полінома, що створюються, прямо вказують, які з

інформаційних символів (включаючи поточний і m попередніх) входять в

лінійну комбінацію, що дає даний символ коду.

символів в групі і має міру, що

не перевищує m.

Ненульові коефіцієнти полінома, що створюються, прямо вказують, які з

інформаційних символів (включаючи поточний і m попередніх) входять в

лінійну комбінацію, що дає даний символ коду.

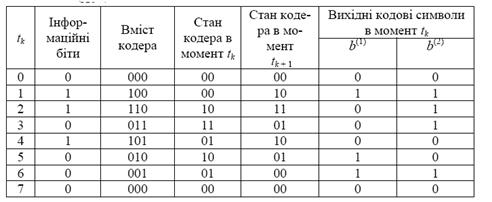

Кодові грати цього коду показані на мал. 1.1. При його складанні

враховано, що кодер містить пам'ять у вигляді дворозрядного регістра. Кожному з

чотирьох можливих станів цього регістра відповідає один з чотирьох вузлів решітки.

Тому лівий символ в позначенні вузла дорівнює останньому інформаційному біту,

вже записаному в регістр. При записі в регістр чергового інформаційного символу

регістр міняє стан на одне з двох сусідніх. Цей перехід позначений ребрами

грат. Порядок вузлів вибраний таким, що при нульовому поточному інформаційному

символі (а=0) перехід в наступний стан відповідає верхньому ребру, а при ![]() = 1 - нижньому.

= 1 - нижньому.

Рисунок 1.1 - Кодові грати

Кожній інформаційній послідовності відповідає певний шлях на кодових гратах і кодова послідовність. Наприклад, вхідним інформаційним бітам 01100 відповідає кодове слово 00 11 01 01 11, якому відповідає на мал. 1.1 шлях, відмічений жирною лінією.

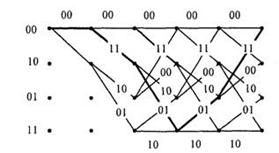

Відомий ряд алгоритмів декодування згортальних кодів. У практичних системах і, зокрема в мобільному зв'язку, як правило, використовується алгоритм Вітербі, що відрізняється простотою реалізації при помірних довжинах кодового обмеження.

Алгоритм Вітербі реалізує оптимальне (максимально правдоподібне) декодування як рекурентний пошук на кодовой гратах шляху, найближчого до послідовності, що приймається. На кожній ітерації алгоритму Вітербі зіставляються два шляхи, що ведуть в даний стан (вузол грат). Найближчий з них до прийнятої послідовності зберігається для подальшого аналізу. Нехай передається нульове кодове слово, а в каналі виникла трикратна помилка, так що прийнята послідовність має вигляд 10 10 00 00 10 00 ... 00 .... Результати пошуку найближчої дороги після прийому 14 елементарних блоків показані на рисунку 1.2.

Рисунок 1.2 - Приклад роботи алгоритму Вітербі

2 Режими зв’язку

2.1 Асинхронний режим

Кажучи про синхронний або асинхронний метод передачі зазвичай мають на увазі передачу по каналу зв'язку між модемами. Модем може працювати з комп'ютером в асинхронному режимі і одночасно з видаленим модемом — в синхронному режимі або навпаки. У такому разі іноді говорять, що модем синхронно-асинхронний або він працює в синхронно-асинхронному режимі [7].

Як правило, синхронізація реалізується одним з двох способів, пов'язаних з тим, як працюють тактові генератори відправника і одержувача: незалежно один від одного (асихронно) або погоджено (синхронно).

Асинхронний режим передачі використовується головним чином тоді, коли передавані дані генеруються у випадкові моменти часу, наприклад користувачем. При такій передачі одержуючий пристрій повинен відновлювати синхронізацію на початку кожного отримуваного символу Такий асинхронний режим часто застосовується при передачі даних по інтерфейсу DTE—DCE.

При передачі даних по каналу зв'язку можливості застосування асинхронного режиму передачі багато в чому обмежені його низькою ефективністю і необхідністю використання при цьому простих методів модуляції, таких як амплітудна і частотна [8].

U

U

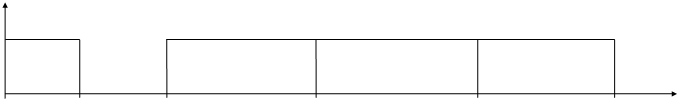

Старт Біт даних Біт контролю Зупинка

t

Рисунок 2.1 - Формат посилання під час асинхронного передавання

Формат асинхронної посилки дозволяє виявляти можливі помилки передачі:

1. Якщо прийнятий перепад, що сигналізує про початок посилки, а по стробу старт-біта зафіксований рівень логічної одиниці, старт-біт вважається помилковим і приймач знову переходить у стан чекання. Про цю помилку приймач може і не повідомляти.;

2. Якщо під час, відведений під стоп-біт, виявлений рівень логічного нуля, фіксується помилка стоп-біту;

3. Якщо застосовується контроль парності, то після посилки біт даних передається контрольний біт. Цей біт доповнює кількість одиничних біт даних до парного або непарного в залежності від прийнятої умови. Прийом байта з помилковим значенням контрольного біта призводить до фіксації помилки.

Контроль формату дозволяє виявляти обрив лінії: при цьому приймаються логічний нуль, що спочатку трактується як старт-біт, і нульові біти даних, потім спрацьовує контроль стоп-біту[3].

При синхронному методі передачі здійснюють об'єднання великого числа символів або байт в окремі блоки або кадрів. Весь кадр передається як один ланцюжок бітів без яких-небудь затримок між восьмибітовими елементами [9].

Щоб приймаючий пристрій міг забезпечити різні рівні синхронізації, повинні виконуватися наступні вимоги:

1. Передавана послідовність бітів не повинна містити довгих послідовностей нулів або одиниць для того, що б приймаючий пристрій міг стійко виділяти тактову частоту синхронізації.

2. Кожен кадр повинен мати зарезервовані послідовності бітів або символів, що відзначають його початок і кінець.

Існує два альтернативні методи організації синхронного зв'язку: символьно- або байт-орієнтовний, і біт-орієнтований. Відмінність між ними полягає в тому, як визначаються початок і кінець кадру. При біт-орієнтованому методі одержувач може визначити закінчення кадру з точністю до окремого біта, а байта (символу) [10].

Окрім високошвидкісної передачі даних власне по фізичних каналах синхронний режим часто застосовується і для передачі по інтерфейсу DTE — DCE. В цьому випадку для синхронізації використовуються додаткові інтерфейсні ланцюги, по яких передається сигнал тактової частоти від відправника до одержувача.

U

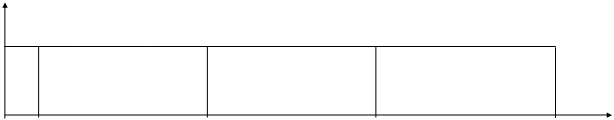

U

Синхросимвол 1 Синхросимвол 2 Біти даних

t

Рисунок 2.2 - Формат посилання під час синхронного передавання

2.2. Напівдуплексний режим

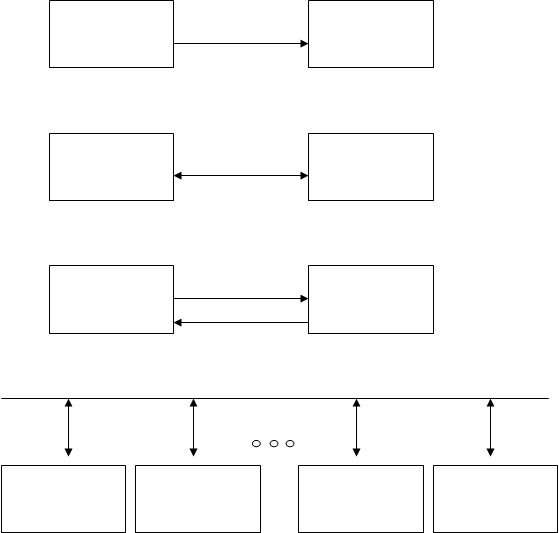

Відомі інтерфейси дозволяють організувати обмін інформацією в симплексному, напівдуплексному, дуплексному режимах. Для випадку зв’язку двох абонентів в симплексному режимі тільки один з двох абонентів може ініціювати в любий момент часу передачу інформації по інтерфейсу (рисунок 2.3, а).

Для випадку зв’язку абонентів у напівдуплексному режимі будь-який абонент може розпочати передачу інформації іншому, якщо лінія зв’язку інтерфейсу при цьому виявляється вільною (рисунок 2.3, б).

Для випадку зв’язку абонентів у дуплексному режимі кожний абонент може розпочати передачу інформації іншому в довільний момент часу (рисунок 2.3, в).

Для

випадку ![]() абонентів

у мультиплексному режимі в довільний момент часу зв’язок може бути здійснено

між парою абонентів у будь-якому, але єдиному напрямі від одного з абонентів до

іншого (рисунок 2.3, г).

абонентів

у мультиплексному режимі в довільний момент часу зв’язок може бути здійснено

між парою абонентів у будь-якому, але єдиному напрямі від одного з абонентів до

іншого (рисунок 2.3, г).

Система міжконтролерного обміну розрахована на обмін інформацією між двома ППІ, причому інформація спочатку з пам’яті одного пристрою передається другому, а потім навпаки.

а)

а)

A B

б)

A B

в)

A B

г)

1 2 n-1 n

а) – симплексний, б) – напівдуплексний,

в) – дуплексний, г) – мультиплексний.

Рисунок 2.3 - Режими обміну інформацією

3 Аналіз елементної бази

3.1 Універсальний синхронно-асинхронний приймач-передавач

Мікросхема КР580ВВ51 являє собою однокристальний програмований пристрій для синхронно-асинхронних приймально-передавальних каналів послідовного зв’язку.

УСАПП перетворює паралельний код, який одержує з шини даних, на послідовний потік символів зі службовими бітами і видає його до каналу зв’язку з різною швидкістю, а також виконує зворотне перетворення.

Приймач-передавач може працювати у п’яти режимах:

- асинхронне передавання;

- асинхронне приймання;

- синхронне передавання;

- синхронне приймання із внутрішньою синхронізацією;

- синхронне приймання із зовнішньою синхронізацією.

![]()

![]()

![]()

![]() Швидкість передавання під

час обміну інформацією у синхронному режимі може сягати 56000 біт/с, у

асинхронному – 9600 біт/с. Довжина слів, що передаються – 5 ... 8 біт.

Швидкість передавання під

час обміну інформацією у синхронному режимі може сягати 56000 біт/с, у

асинхронному – 9600 біт/с. Довжина слів, що передаються – 5 ... 8 біт.

![]()

![]()

![]()

![]()

![]()

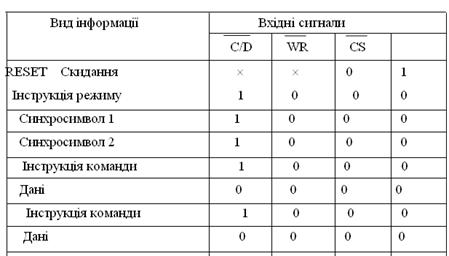

![]() Основними сигналами управління

є: WR, RD, C/D, CS. Вхідні сигнали WR та RD визначають напрямок потоку

інформації, що передається з шини даних мікропроцесора до УСАПП чи навпаки.

Вхідний сигнал C/D разом із сигналами WR, RD та CS визначає вид інформації, що

поступає до мікросхеми чи до каналу даних.

Основними сигналами управління

є: WR, RD, C/D, CS. Вхідні сигнали WR та RD визначають напрямок потоку

інформації, що передається з шини даних мікропроцесора до УСАПП чи навпаки.

Вхідний сигнал C/D разом із сигналами WR, RD та CS визначає вид інформації, що

поступає до мікросхеми чи до каналу даних.

Послідовність записування інструкції команди та інструкції режиму, синхросимволів та даних для запуску мікросхеми наведена у таблиці 3.1. При цьому синхросимвол може бути один чи обидва взагалі відсутні, що визначається інструкцією режиму.

Таблиця 3.1 - Послідовність завантаження УСАПП

З таблиці 3.1 видно, що безпосередньо після скидання потрібно записати інструкцію режиму, тобто до регістра режиму записується перше слово управління для синхронного чи асинхронного режиму.

Оскільки в технічному завданні на курсовий проект задано асинхронний режим передачі, то слово управління буде мати вигляд, наведений на рис.3.1:

Рисунок 3.1 - Формат інструкції для асинхронного режиму

Відповідно до наведенної структури виберемо формат слова управління, наведений у табл. 3.2:

Таблиця 3.2 - Формат слова управління

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

Розряди D0 та D1 визначають асинхронний режим. Це поле також визначає швидкість приймання та передавання інформації, яку ми вибираємо рівною 1:1.

Розряди D2 та D3 визначають довжину (кількість бітів даних) слова, що передається чи приймається.

Розряди D4 та D5 здійснюють управління контролем парності. Біт контроля парності додається до бітів даних (не входить у довжину слова). Контроль парності не використовується.

Розряди D6 та D7 визначають кількість стоп-бітів, які вводяться після біту контролю і призначені для фіксації закінчення посилання даних. Довжину стоп-біта вибираємо рівною півтора. Після запису інструкції режиму записується інструкція команди, формат якої наведений на рисунку 3.2.

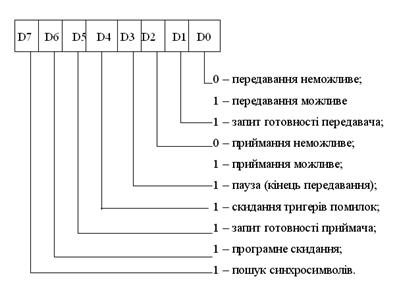

Рисунок 3.2 - Формат інструкції команд

У системах передавання даних часто необхідно контролювати стан сигналів під час виконання операції. Формат регістра станів наведений на рисунку 3.3.

Рисунок 3.3 - Формат регістра стану

Біт D4 встановлюється в одиницю у випадках:

- читання наступної кодової комбінації з лінії зв’язку, коли попередня комбінація мікропроцесором зчитана не була;

- у синхронному режимі роботи із внутрішньою синхронізацією, коли попередня кодова комбінація відповідала першому синхросимволу, а наступна не відповідає другому синхросимволу;

- під час читання даних чи стану у випадку внутрішнього пересилання інформації чи синхросимволів.

Помилки не переривають роботи мікросхеми. Тригери встановлюються до початкового стану інструкцією команди. Читання стану дозволяє використовувати дану мікросхему не лише у режимі переривань, але й у режимі програмного опитування прапорів.

Прямим аналогом цієї мікросхеми є I8251 фірми Intel Corp .

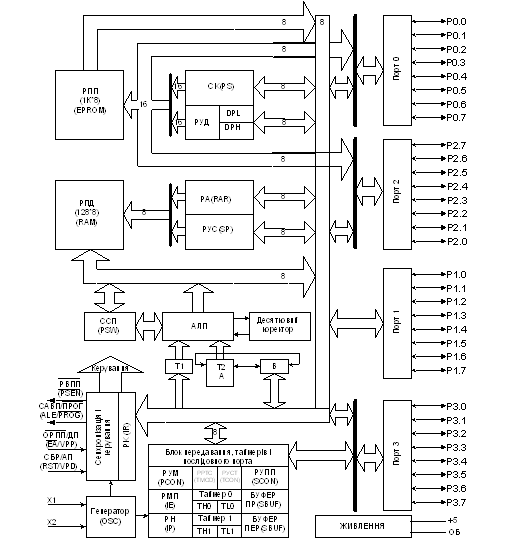

3.2 Мікроконтролер КМ1816ВЕ51

З урахуванням вимог технічного завдання, для виконання пристрою міжконтролерного обміну інформацією, її кодування та декодування, а також запису інформації доцільно використати мікропроцесор КМ1816ВЕ51.

Мікроконтролер виконаний на основі високорівневої N-МОП технології і випускається в корпусі ВІС, що має 40 зовнішніх виводів. Цокольовка корпусу МК51 і найменування виводів показані на рисунку 3.4.

Для роботи МК51 потрібно одне джерело електроживлення +5 В. Через чотири порта що програмуються введення/виводу МК51 взаємодіє із середовищем у стандарті ТТЛ-схем із трьома станами виходу.

Основу структурної схеми МК51 (рисунок 3.5) утворює внутрішня двонаправлена 8-бітна шина, що зв'язує між собою всі основні вузли і пристрої:

- резидентна пам'ять,

- АЛП,

- блок регістрів спеціальних функцій,

- пристрій керування

- порти введення/виводу.

Арифметично-логічний пристрій.

8-бітне АЛП може виконувати арифметичні операції додавання, віднімання, множення і ділення; логічні операції І, АБО, виключаєче АБО, а також операції циклічного зсуву, скиду, інвертування і т.п. У АЛП є програмно недоступні регістри Т1 і Т2, призначені для тимчасового збереження операндів, схема десяткової корекції і схема формування ознак.

Найпростіша операція додавання використовується в АЛП для інкрементування вмісту регістрів, просування регістра вказівника даних і автоматичного обчислення наступної адреси РПП. Найпростіша операція віднімання використовується в АЛП для декрементування регістрів і порівняння змінних.

Найпростіші операції автоматично утворять "тандеми" для виконання в АЛП таких операцій, як, наприклад, інкрементування 16-бітних реєстрових пар.

В АЛП реалізується механізм каскадного виконання найпростіших операцій для реалізації складних команд. Так, наприклад, при виконанні однієї з команд умовної передачі керування по результату порівняння в АЛП тричі інкрементується СК, двічі виконується читання з РПД, виконується арифметичне порівняння двох змінних, формується 16-бітна адреса переходу і приймається рішення про те, робити або не робити перехід по програмі. Всі перераховані операції виконуються в АЛП усього лише за 2 мкс.

Пам'ять програм і пам'ять даних, розміщені на кристалі МК51 фізично і логічно розділені, мають різноманітні механізми адресації, працюють під керуванням різноманітних сигналів і виконують різні функції.

Пам'ять програм (ПЗП або СППЗП) має ємність 4 Кбайта і призначена для збереження команд, констант, керуючих слів ініціалізації, таблиць перекодування вхідних і вихідних змінних і т.п. РПП має 16-бітну шину адреси, через яку забезпечується доступ із лічильника команд або з регістра-вказівника даних. Останній виконує функції базового регістра при непрямих переходах по програмі або використовується в командах, що оперують із таблицями.

Пам'ять даних (ОЗП) призначена для збереження змінних у процесі виконання прикладної програми, адресується одним байтом і має ємність 128 байт.

Вхідні сигнали для МК51 можуть формуватися ТТЛ-схемами або n-МОП-схемами. Допустимо використання в якості джерела сигналів для МК51 схем із відкритим колектором або відкритим стоком. Проте при цьому час зміни вхідного сигналу при переході з 0 у 1 виявиться сильно затягнутим.

. Звертання до портів введення/виводу можливо з використанням команд, що оперують із байтом, окремим бітом і довільною комбінацією біт. При цьому в тих випадках, коли порт є одночасно операндом і місцем призначення результату, пристрій керування автоматично реалізує спеціальний режим, що називається "читання- модифікацію-запис". Цей режим звертання припускає введення сигналів не з зовнішніх виводів порту, а з його регістра-засувки, що дозволяє виключити неправильне зчитування раніше виведеної інформації.

Рисунок 3.4 – Структурна схема МК51

4 Розробка структурної схеми

Структурна схема знаходиться у додатку В, складається з таких блоків:

1) лінія зв’язку;

2) перетворювач уніполярної напруги в біполярну;

3) перетворювач біполярної напруги в уніполярну;

4) згортковий кодер;

5) згортковий декодер;

6) пристрій введення/виведення;

7) тригер (для запам’ятовування стану);

8) лічильник;

9) пристрій управління;

10) мікроконтролери.

В основі пристрою лежить система передачі інформації, яка складається з вищеописаних блоків. Вона складається з приймальної частини, каналу зв’язку і передавальної частини. Передавальна частина складається з мікроконтролера, в якому зберігається інформація, яку потрібно передати, пристрою управління, який керує зчитуванням даних з мікроконтролера, пристрою введення/виведення (IOS), який представляє собою УСАПП Intel 8251, згорткового кодера, який кодує інформацію згортковим кодом, який може виправляти помилки, перетворювача уніполярної напруги в біполярну згідно індивідуального завдання, схеми зворотнього зв’язку, потрібної для того, щоб впевнитись, що повідомлення було прийнято, яка складається зі схеми вимірювання часу, двох тригерів, лічильника і ця схема з’єднана з пристроєм управління.

Лінія зв’язку представляє собою самостійний елемент і в даній роботі вона розглядається як єдиний блок в спрощеному вигляді.

Приймальна частина складається з перетворювача біполярної напруги в уніполярну, щоб отримати сигнали, які сприймають цифрові мікросхеми, згорткового декодера, щоб декодувати інформацію, закодовану кодером і виявити помилки, якщо вони є , мікроконтролера, в який записується інформація в разі її успішного прийому, схеми зворотнього зв’язку, яка передає передавальній стороні сигнали про те, що інформація успішно і правильно прийнята, або прийнята неправильно. Вона складається з двох тригерів і формувача повідомлення.

5 Розробка функціональної схеми

Інформація, призначена для передавання знаходиться в мікроконтролері, де чекає своєї черги на передавання. З мікроконтролера інформація по 8 біт передається до входу згорткового кодера, де вона кодується згортковим кодом для виправлення помилок і передається на вхід ТхD УСАПП. У якості пристрою введення-виведення УСАПП вибрано І8251. Після формування повідомлення в асинхронному режимі сигнал перетворюється з уніполярного в біполярний. Цей перетворювач сигналів містить у собі тригер, 2 мікросхеми «АБО», один інвертор і підсилювач з коефіцієнтом підсилення 2.4 і суматор на операційному підсилювачі.

Схема зворотного звязку реалізована, як показано в додатку В: в основі її лежить схема вимірювання часу для порівняння прийнятого сигналу з еталонним. Можливі 2 варіанти: або прийнятий сигнал менше еталонного, або довше. У першому випадку це означає, що потрібно повторити біт інформації, в другому-що можна передавати наступний біт. Лише після спрацювання схеми зворотного звязку і отримання сигналу про успішне передавання може початись передавання наступного біта. Для зафіксування стану успішного прийняття інформації використовуються 2 тригера. Пристрій управління для керування мікроконтролером використовуються два лічильника-один перемикається при отриманні сигналу про те, що треба передавати біт, а інший послідовно генерує 8 імпулісів для зчитування 8 біт.

На приймальній стороні сигнал поступає на перетворювач біполярної напруги в уніполярну, який реалізований на 2-х діодах і одному підсилювачі з коефіцієнтом підсилення -1 і суматора на операційному підсилювачі, який також послаблює сигнал в 2.4 рази. Після перетворення інформація поступає на згортковий декодер, де вона декодується, виправляються помилки. Після декодування сигнал поступає на вхід RxD і записується по мікроконтролеру. Якщо інформація не записалась(наприклад-виникнення помилки переповнення чи парності) схема зворотного звязку сигналізує про відповідну помилку. Тригер встановлюється в 1, і одновібратор генерує імпульс тривалістю 0.3 мс. Якщо помилки не виникло і можна передавати наступний біт, генерується імпульс тривалістю 0.5 біт. Один з цих імпульсів відсилається до лінії звязку.

6 Розробка принципової схеми

У якості операційних підсилювачів в схемі вибрано К1401УД1. Цей ОП вимагає двополярного живлення -5В - +5В.

У якості мікросхем логічних «АБО» вибрано мікросхеми КР1533ЛИ6 з живленням від 0 до +5В, яка містить 4 «АБО».

У якості мікросхем логічних «І» вибрано мікросхеми КР1533ЛИ1 з живленням від 0 до +5В, яка містить 4 «І».

У якості мікросхем Т-тригерів обрано мікросхеми КР1533ТМ7 на основі D-тригерів з живленням від 0 до +5В, яка містить 4 тригера.

У якості пристрою введення-виведення УСАПП вибрано І8251.

7 Вибір та обґрунтування мови програмування

Існує велика кількість мов програмування, які застосовуються при роботі з різноманітними мікропроцесорами, мікроконтролерами та персональними комп’ютерами. Мови програмування для мікро-ЕОМ можна розділити на три основних рівні: машинні, алгоритмічні високого рівня і асемблера.

На самому нижньому рівні знаходяться машинні мови програмування. Їх основним недоліком є те, що будучи мовами цифр, вони незручні для опису обчислювальних процесів і тому потребують від програмістів великих зусиль при написанні і налагодженні програм. Перевагами машинної мови є те, що для програмування на ній необхідні знання тільки системи команд ЕОМ, а для виконання складених таким чином програм обчислювальна машина не потребує ніяких трансляторів. Крім того, при використанні машинної мови можна досягнути максимальної гнучкості в реалізації технічних можливостей ЕОМ.

Алгоритмічні мови високого рівня (наприклад Паскаль) займають верхнє положення в ієрархії мов програмування. Будучи наближеними до звичної математичної нотації і в ряді випадків забезпечуючи природну форму опису обчислювальних процесів, вони доволі прості і зручні в програмуванні, але не завжди дозволяють в повній мірі реалізувати технічні можливості ЕОМ, а результуючі машинні програми, отримані після трансляції програм з алгоритмічних мов, зазвичай неефективні з точки зору об’єму або швидкодії. Недоліком цих мов також є те, що їх застосування передбачає наявність транслятора, який є складним програмним комплексом. Але внаслідок своїх незаперечних переваг мови високого рівня широко застосовуються в програмуванні для різних класів ЕОМ, в тому числі і для мікро-ЕОМ.

Мова DELPHI, забезпечуючи можливість символічних імен в програмі і позбавляючи програміста від стомлюючої роботи по розподілу пам’яті ЕОМ для змінних і констант, суттєво полегшує роботу програміста і підвищує його продуктивність у порівнянні з програмуванням на машинній мові. Мова DELPHI дозволяє також гнучко і повно реалізовувати технічні можливості ЕОМ. В середовищі DELPHI реалізовано зручний та потужний компілятор програм, необхіднй для мов високого рівня, а результуюча машинна програма на виході DELPHI може бути такою ж ефективною, як і програма, яку зразу написали на машинній мові. Тому не дивно, що середовище програмування DELPHI набуло широкого вжитку серед програмістів.

Мова програмування Паскаль є мовою помірної складності і містить в той самий час розвинені засоби для організації і обробки різноманітних структур даних і є досить досконалим інструментом для створення надійного програмного забезпечення.

Таким чином, проаналізувавши вище сказане, було вирішено реалізувати програмну частину даного курсового проекту на мові низького рівня – Ассемблер.

Висновки

В результаті виконання даного завдання було розроблено технічні засоби міжконтролерного обміну та докуменацію до нього, які задовольняють усім вимогам до курсового проекту.

Курсовий проект складається з 7 розділів.

В першому розділі було приведено основні відомості стосовно загорткових кодів.

В другому розділі охарактеризовано режими передачі даних..

Третій розділ присвячений вибору елементної бази..

В четвертому розділі описано процес розробки структурної схеми.

В п’ятому розділі описано функціональну схему.

В шостому розділі описано принципову схему.

Сьомий розділ присвячений вибору мови програмування та розробці алгоритмів.

Література

1. Разработка и оформление конструкторской документации радиоэлектронной аппаратуры: Справочник / Романычева Э.Т., Иванова А.К., Куликов А.С. и др.; Под ред. Романычевой Э.Т.- М.: Радио и связь, 1989.

2. Воробьёв Н.И. Проектирование электронных устройств. – М.: Высшая школа, 1989.

3. Усатенко С.Т., Каченюк Т.К., Терехова М.В. Выполнение электрических схем по ЕСКД.- М.: Издательство стандартов, 1989.

4. Хоровиц П., Хилл У. Искусство схемотехники: В 2-х томах.- М.: Мир, 1986.

5. Справочник по единой системе конструкторской документации / под ред. Степанова Ю.И.- Харьков: Прапор, 1979.

Додатки

Додаток А

(обов’язковий)

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут автоматики, електроніки та комп’ютерних систем управління

Факультет автоматики та комп’ютерних систем управління

Кафедра автоматики та інформаційно-вимірювальної техніки

|

Затверджено Керівник А.Я. Кулик ________________________ “____”_____________ 2009 р. |

||

|

Розроблено Студент гр. 4АС-06 Бондар В.А. ________________________ “____”_____________ 2009 р. |

ТЕХНІЧНЕ ЗАВДАННЯ

на виконання курсового проекту

“Технічні засоби обміну інформацією для банківської системи з визначенням та виправленням помилок”

1. Найменування продукту, що розробляється: технічні засоби обміну інформацією для банківської системи з визначенням та виправленням помилок.

2. Галузь використання продукту: для обміну інофрмацією між здавачами, сенсорами та комп’ютерами, розташовиними на невеликій відстані; для звязку двох систем, інтерфейси яких не дозволяють в стандартній комплектації обмінюватися інформацією на відстані, та для здешевлення та спрощення лінії звязу.

3. Підстава для розробки продукту:

3.1. Навчальний план спеціальності 7.091401.

3.2. Робоча програма дисципліни “ Основи техніки збирання, оброблювання та предавання інформації ”.

4. Індивідуальне завдання на курсовий проект.

5. Вимоги до програмного продукту:

5.1. Операційна система – Windows ХР, NT.

5.2. Вимоги до надійності – відсутність програмних збоїв.

6. Все програмне забезпечення та супроводжуюча технічна документація повинні задовольняти наступним ГОСТам:

ГОСТ 19.701-90

ИСО 5807-85 – ГОСТ на розробку програмних документів, схеми алгоритмів програм, даних та системи.

ГОСТ 19.781-74 – вимоги до розробки програмного забезпечення

ГОСТ 19.101-77 (СТ СЭВ 1626-79) – держстандарт на розробку програмної документації, видів програм та програмних документів.

ГОСТ 19.401-78 – текст програми. Вимоги до змісту та оформлення.

ГОСТ 19.106-78 – вимоги до програмної документації.

ГОСТ 7.1-84 та ДСТУ 3008-95 – розробка технічної документації.

7. Стадії та етапи розробки:

7.1. Реєстрація навчального курсу – ___________.

7.2. Відкриття курсу до розробки – ___________.

7.3. Підготовка занять – ___________.

7.4. Активація курсу – ___________.

7.5. Оформлення пояснювальної записки – ___________.

8. Порядок контролю та приймання курсового проекту:

Отримання завдання на виконання курсового проекту – __________.

Термін здачі курсового проекту на перевірку – до ___________.

Термін захисту курсового проекту – до ___________.

Додаток Г

(обовязковий)

| Позн. | Найменування | Кіл | Примітки | ||||||||||

| Аналогові мікросхеми | |||||||||||||

| DA1-DA2 | К1401УД1 | 2 | |||||||||||

| Цифрові мікросхеми | |||||||||||||

| DD1 | КР15ИП6 | 1 | |||||||||||

| DD2 | КФ1174ПП1 | 1 | |||||||||||

| DD3 | І8251 | 1 | |||||||||||

| DD4 | КМ1816ВЕ51 | 1 | |||||||||||

| Резистори | |||||||||||||

| R1-R6 | 1 кОм | 5 | |||||||||||

| R7 | 2.4 кОм | 1 | |||||||||||

| Діоди | |||||||||||||

| VD1-VD2 | 2 | ||||||||||||

| Розєми | |||||||||||||

| Х2 | 1 | ||||||||||||

| 08-02.ОТЗОПІ.059. 00.000 ПЗ | |||||||||||||

| Зм. | Арк | № докум. | Підпис | Дата | |||||||||

| Розроб. | Бондар В.А. |

Приймач Пояснювальна записка |

Літ. | Аркуш | Аркушів | ||||||||

| Перевір. | Кулик А.Я. | ||||||||||||

| Реценз. | ВНТУ гр. 4АС-06 | ||||||||||||

| Н. Контр. | Кулик А.Я. | ||||||||||||

| Затверд. | |||||||||||||

| Позн. |

Найменування |

Кіл. |

Примітки |

||||||||||

| Аналогові мікросхеми | |||||||||||||

| DA1-DA2 | К1401УД1 | 2 | |||||||||||

| Цифрові мікросхеми | |||||||||||||

| DD1 | КМ1816ВЕ51 | 1 | |||||||||||

| DD2 | І8251 | 1 | |||||||||||

| DD3 | КФ1174ПП1 | 1 | |||||||||||

| DD4 | КР1533КП2 | 1 | |||||||||||

| DD5 | КР1533ТМ7 | 1 | |||||||||||

| DD6 | КР1533ЛИ1 | 1 | |||||||||||

|

DD7, DD8 |

КР1533ЛИ6 | 2 | |||||||||||

| Резистори | |||||||||||||

| R1-R4 | 1 кОм | 4 | |||||||||||

| R5 | 2.4 кОм | 1 | |||||||||||

| Розєми | |||||||||||||

| Х1 | 1 | ||||||||||||

| 08-02.ОТЗОПІ.059. 00.000 ПЗ | |||||||||||||

| Зм. | Арк | № докум. | Підпис | Дата | |||||||||

| Розроб. | Бондар В.А. |

Передавач Пояснювальна записка |

Літ. | Аркуш | Аркушів | ||||||||

| Перевір. | Кулик А.Я. | ||||||||||||

| Реценз. | ВНТУ гр. 4АС-06 | ||||||||||||

| Н. Контр. | Кулик А.Я. | ||||||||||||

| Затверд. | |||||||||||||

Додаток Д (обов’язковий)

Додаток Е

(обов’язковий)

Лістинг програми

MOV AL, 0B12H

OUT 0EH, AL

Введення інформації

MOV AL, 09

OUT 0EH, AL

CALL DELAY

MOV AL, 08

OUT 0EH, AL

DELAY: MOV CX, 134

D: LOOP D

RET

M1: IN AL, 0CH

AND AL, 00001000B

JK M1

ANI 00001111

IN AL, 08H

MOV R, AL

ANI 1111 0000

IN AL, 08H

MOV R, AL

MOV AL, 0B12H

OUT 0EH, AL

Виведення інформації

MOV AL, 03

OUT 0EH, AL

CALL DELAY

MOV AL, 01

OUT 0EH, AL

DELAY: MOV CX, 134

D: LOOP D

RET

M1: IN 0CH, AL

AND AL, 00001000B

JK M1

MOV AL , R

ANI 00001111

OUT AL, 0АH

MOV AL , R

ANI 1111 0000

OUT AL, 0АH