Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Курсовая работа: Схема електрична принципова модуля на базі 8-розрядного мікропроцесора

Курсовая работа: Схема електрична принципова модуля на базі 8-розрядного мікропроцесора

Міністерство освіти і науки України

ДЕРЖАВНИЙ ВИЩИЙ НАВЧАЛЬНИЙ ЗАКЛАД

"КИЇВСЬКЙ НАЦІОНАЛЬНИЙ ЕКОНОМІЧНИЙ УНІВЕРСИТЕТ ІМЕНІ ВАДИМА ГЕТЬМАНА"

РОМЕНСЬКИЙ КОЛЕДЖ

Спеціальність: 5.091504 "Обслуговування комп’ютерних та інтелектуальних систем та мереж"

Курсовий проект з предмету:

Мікропроцесорні системи

Тема: "Розробити схему електричну принципову модуля

на базі 8-розрядного МП"

РК КНЕУ. КП.5.091504.009 ПЗ

Перевірив викладач Шокота Т.А.

Виконав:

студент гр. К 3-2 Лакиза Н.С.

2007

Зміст

Вступ. 3

1. Загальний розділ. 6

1.1. Призначення проектуємого пристрою.. 6

1.2. Технічні характеристики. 10

1.3. Розробка і обґрунтування схеми електричної структурної 11

2. Спеціальний розділ. 13

2.1. Вибір і обґрунтування елементної бази. 13

2.2. Принцип роботи окремих ВІС з використанням часових діаграм.. 16

2.3. Принцип роботи пристрою згідно схеми електричної принципової 21

3. Експлуатаційний розділ. 23

3.1. Ініціалізація програмуємих ВІС.. 23

3.2. Тест перевірки окремих вузлів або пристрою.. 23

3.3. Розрахунок надійності пристрою.. 26

Література. 30

Вступ

Безупинне удосконалення технології і схемотехніки великих інтегральних мікросхем (ВІС) обумовило створення і розвиток одних з найбільш універсальних ВІС - мікропроцесорів. До сьогоднішнього часу вітчизняною промисловістю і закордонними фірмами випускається велике число комплектів мікропроцесорних ВІС, що відрізняються швидкодією, потужністю споживання, розрядністю й іншими характеристиками, а також функціональним набором схем у комплекті. Функціональний склад комплектів мікропроцесорних ВІС і їх основні характеристики визначалися на основі аналізу різних варіантів застосування мікропроцесорів і оптимізації алгоритмів керування з урахуванням вимог до продуктивності й обсягу адресуємої пам'яті.

Високий рівень технічних характеристик мікропроцесорних ВІС і порівняно низька вартість у розрахунку на одиницю оброблюваної інформації стимулювали швидке впровадження мікропроцесорів у побутову, промислову і спеціальну радіоелектронну апаратуру.

Мікропроцесор (МП) - програмно-управляючий пристрій, призначений для обробки цифрової інформації і керування процесом цієї обробки, виконаний у виді однієї (чи декількох) інтегральної схеми з високим ступенем інтеграції електронних елементів.

Продуктивність мікропроцесорів безупинно зростає в міру удосконалення мікроелектронної технології й архітектури. У найбільш досконалих мікропроцесорах вона вже з початку 80-х років не поступається продуктивності процесорам звичайних міні-ЕОМ середньої обчислювальної потужності.

Процесори ЕОМ мають складну логічну структуру і містять велику кількість електронних елементів з безліччю розгалужених зв'язків між ними. Для підвищення продуктивності процесора необхідно розвивати всі його апаратні ресурси. Можливості однокристальних мікропроцесорів визначає мікроелектронна технологія на визначеному рівні розвитку. Тому, щоб збільшити продуктивність процесорів, використовують їх реалізацію у вигляді багатокристальних, а також секційних багатокристальних мікропроцесорів.

Багатокристальні МП можна одержати в тому випадку, коли відбувається поділ логічної схеми процесора на окремі функціонально закінчені частини, кожна з яких реалізується у виді інтегральної схеми.

Необхідність виконання складних функцій керування призвела до створення мікроконтролерів - керуючих пристроїв, виконаних на одному чи декількох кристалах. Мікроконтролери виконують функції логічного аналізу і керування (тому за рахунок виключення арифметичних операцій можна зменшити їхню апаратну складність чи розвинути функції логічного керування).

Архітектура мікропроцесора - функціональні можливості апаратних електронних засобів мікропроцесора, використовувані для представлення даних, машинних операцій, опису алгоритмів і процесів обчислень.

Архітектура поєднує апаратні, мікропрограмні і програмні засоби обчислювальної техніки і дозволяє чітко виділити те, що, при створенні конкретної мікропроцесорної системи і використанні можливостей мікропроцесорного комплекту, ВІС повинні бути реалізовані користувачем програмним способом і додатковими апаратними засобами.

Розробляючи програмне забезпечення для мікро-ЕОМ, програміст повинен знати архітектурні особливості і технічні характеристики мікро-ЕОМ. Ця вимога необхідна при використанні мови асемблера, але вона може виявитися істотною і при використанні мови високого рівня. Однак програміст може знатися в апаратному забезпеченні, і тим більше в схемотехнічних елементах мікро-ЕОМ не настільки детально, як інженер-розроблювач мікропроцесорних пристроїв. На відміну від останнього програміст може мати потребу в з'ясуванні і розумінні лише елементів і характеристик обчислювальної машини, що явно відбиваються в програмах і (або) повинні бути враховані при розробці і виконанні програм. До таких елементів і характеристик мікро-ЕОМ варто віднести, зокрема, число й імена програмно-доступних регістрів, розрядність машинного слова, систему команд, доступний розмір і адреси оперативної пам'яті, швидкодію процесора, схему обробки переривань, способи адресації оперативної пам'яті і зовнішніх пристроїв. Сукупність подібних зведень являє собою модель мікро-ЕОМ з погляду програміста.

Для ефективного використання мікро-ЕОМ споживач повинен володіти мовами програмування різного рівня. Задачі системного програмування, наприклад, досить часто вимагають застосування мови асемблера, яка дає можливість найбільш повно і раціонально використовувати апаратні і програмні ресурси мікро-ЕОМ.

У даному курсовому проекті розроблено схему електричну принципову процесорного модуля з використанням мікропроцесора КР580ВМ80А

1. Загальний розділ

1.1. Призначення проектуємого пристрою

У курсовому проекті прийняті наступні скорочення:

БА - буфер адреси;

БД - буфер даних;

ВІС - велика інтегральна схема;

ОС - обчислювальна система;

ГТІ - генератор тактових імпульсів;

ЗП - запам'ятовуючий пристрій;

ІС - інтегральна схема;

МС - мікросхема;

МА - магістраль адреси;

МД - магістраль даних;

МК - магістраль керування;

МП - мікропроцесор;

МПС - мікропроцесорна система;

ОЗП - оперативно-запам'ятовуючий пристрій;

ПДП - прямий доступ у пам'ять;

ПЗП - постійно-запам'ятовуючий пристрій;

ЦП - центральний процесор;

ПВВ - пристрій введення-виведення;

ЕОМ - електронно-обчислювальна машина;

ЧТП - читання пам'яті;

ЗПП - запис у пам'ять;

ЗПВВ - запис у пристрої введення/виведення;

ППРЕ - підтвердження переривання

Розробка архітектури МПС.

Проектування нової мікро-ЕОМ звичайно починається з опису її архітектури, що представляє собою модель мікро-ЕОМ з точки зору програміста. Модель у процесі проектування перетворюється в структуру мікро-ЕОМ, що визначає склад, призначення і взаємозв'язки необхідних апаратурних компонентів, що реалізують бажану архітектуру.

Останнім часом найбільше поширення одержав принцип модульної організації обчислювальних систем. Серед способів організації зв'язку елементів всередині модулів і між модулями в системі можна виділити два: за допомогою довільних зв'язків, що реалізують принцип "кожний з кожним", і за допомогою упорядкованих зв'язків (магістральний), що дозволяє мінімізувати число зв'язків.

Найбільш розповсюдженою є схема мікро-ЕОМ, що має дві чи три загальні магістралі, до яких під впливом пристрою керування можуть по черзі підключатися вхідні в мікропроцесор вузли. Така структура вимагає обмеженого числа зовнішніх контактів, але обмін інформацією між вузлами і блоками повинен здійснюватися у визначеній послідовності.

У мікро-ЕОМ процесор будується на ВІС, що утворює базовий МП-комплект. Процесор мікро-ЕОМ може бути реалізований у вигляді однієї (однокристальний мікропроцесор) чи декількох ВІС (багатокристальний мікропроцесор).

Відповідно до розробки спеціалізованих ІС для різних блоків мікро-ЕОМ структурна схема її може бути представлена як сукупність

функціональних блоків, з'єднаних між собою відповідно до вимог інтерфейсів. У приведеній схемі обробку інформації здійснює мікропроцесор, синхронізуємий тактовими імпульсами пристрою синхронізації. Обмін інформацією між мікропроцесором і іншими блоками мікро-ЕОМ здійснюється по трьох магістралях: адресної, даних і керуючої.

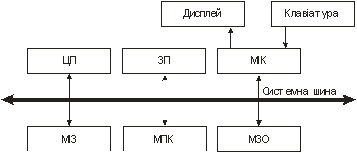

Структура МП системи представлена на рисунку 1.1.1.

Рисунок 1.1.1. – Узагальнена структура мікропроцесорної системи

На рисунку 1.1.1. прийнято наступні умовні позначення:

ЦП - центральний процесор на основі мікропроцесора;

ЗП - напівпровідникова пам'ять (ОЗП, ПЗП);

МІК - модуль інтерфейсу користувача;

МКП - модуль контролерів переривань і ПДП;

МІЗ - модуль інтерфейсу зв'язку;

МЗО - модуль зв'язку з об'єктом;

Системна шина містить у собі три магістралі: адресну, даних і керування.

проводиться звертання до пристроїв пам'яті, введення/виведення й інших зовнішніх пристроїв, підключених до мікропроцесора. Оброблена інформація і результати обчислень передаються по магістралі даних (МД). Магістраль керування (МК) передає керуючі сигнали на всі блоки мікро-ЕОМ, та настроює на потрібний режим пристрої, що беруть участь у виконуванні команд.

Використання в мікро-ЕОМ трьох магістралей забезпечує високу швидкодію і спрощує процес обчислень. Можлива побудова мікро-ЕОМ з однією чи двома магістралями, по яких послідовно передаються код адреси й оброблювана інформація, але при цьому збільшується час виконання команд й ускладнюється організація обміну даними між вузлами.

Вибір мікропроцесора і системного контролера.

Одним з основних критеріїв при виборі МП є швидкодія. Так як до проектованої системи не пред'являються високі вимоги, то можна вибрати мікропроцесор із середньою швидкодією. Виберемо мікропроцесор із МПК серії КР580.

Мікропроцесорний комплект серії КР580 є одним з розповсюджених комплектів ВІС, що дозволяє створювати ефективні обчислювальні пристрої, орієнтовані на реалізацію обчислювальних задач і використання їх як пристроїв керування. Основу комплекту складає однокристальний МП КР580ВМ80. Крім МП до складу серії КР580 входить велике число ВІС, що дозволяють відносно просто підключати до МП різні пристрої, організовувати швидкий обмін інформацією між блоками ЕОМ. Розглянемо особливостей побудови мікро-ЕОМ на прикладі МПК серії КР580.

Мікропроцесорний комплект КР580 містить у собі мікросхеми:

Мікропроцесорна ВІС.

Програмований пристрій введення-виведення рівнобіжної інформації різного формату КР580ВВ55.

Програмований блок пріоритетного переривання КР580ВН59.

Програмований пристрій прямого доступу до пам'яті КР580ВТ57.

Інтегральний таймер КР580ВИ53.

Універсальний синхронно-асинхронний програмований прийомо-передавач КР580ВВ51.

Програмований контролер клавіатури КР580ВВ79.

Системний контролер КР580ВК28.

Схеми виконані по n-МОП технології, вхідні і вихідні сигнали відповідають рівням роботи ТТЛ-схем. Мікро-ЕОМ, побудована на базі комплекту, працює з тактовою частотою до 2 Мгц. Схеми програмуються за допомогою фіксованого набору команд МП ВІС КР580ВМ80.

Мікропроцесорна ВІС КР580ВМ80 являє собою однокристальний 8-розрядний МП із двома магістралями: однонапрямленою 16-розрядною адресною магістраллю (МА), двонаправленою 8-розрядною магістраллю даних (МД), і 12 сигналами керування (шість вхідних і шість вихідних). МП застосовується як центральний процесор у пристроях обробки даних і керування. Канал адреси забезпечує пряму адресацію зовнішньої пам'яті обсягом до 65535 байт, 256 пристроїв введення і 256 пристроїв виведення.

Мікропроцесорна ВІС розрахована на виконання логічних і арифметичних операцій з 8-розрядними числами в двійковій і десятковій системах числення, а також операцій з подвійною розрядністю (з 16-розрядними числами).

Як системний контролер буде використовуватися ВІС КР580ВК28, яка необхідна для фіксації слова - стану МП, вироблення системних керуючих сигналів, буферизації шини даних МП і керування напрямком передачі даних.

1.2. Технічні характеристики

Проектована МП система має наступні основні технічні характеристики:

Елементна база - мікросхеми серій К580.

Базовий комплект - ВІС серії К580.

Центральний процесор - КР580ВМ80А.

Розрядність шини адреси - 1 б біт.

Розрядність шини даних - 8 біт.

Число команд - 244.

Формати команд - нуль-, одне - і двохадресні.

Розрядність команд - 8,16, 24 біт.

Формат даних - двійкові числа з фіксованою комою.

Способи адресації - пряма, непряма, безпосередня, неявна

Число 8-розрядних регістрів загального призначення - 6.

Час виконання команд додавання R-R - не більш 2 мкс.

Число адресуємих регістрів введення-виведення - 256.

Обсяг адресуємої пам'яті - 64 К байт.

Ємність ПЗП - 16 К байт,

Ємність ОЗП - 64 К байт.

Продуктивність - 110 тис. оп/с.

Система переривань - програмно-пріоритетна з 8 лініями апаратного переривання.

Час реакції на переривання - 18 мкс.

Параметри вхідних і вихідних сигналів сумісні з ТТЛ-рівнями.

1.3. Розробка і обґрунтування схеми електричної структурної

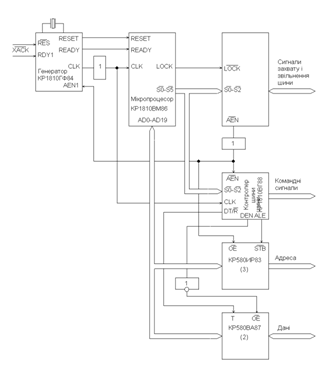

Схему електричну структурну пристрою розглянемо на прикладі мікросхеми КР1810ВБ89 (рисунок 1.3.1) призначеної для реалізації пріоритетного безконфліктного доступу до системної шини мультипроцесорної системи. Арбітр шини дешифрує стан мультипроцесора, виробляє керуючі сигнали для організації доступу до шини типу Мультибас і керує контролерами шини й регістрами для фіксації адреси.

Арбітр шини складається з наступних функціональних блоків: дешифратора станів, що декодує стан мікропроцесора і формує сигнали, що надходять на схеми арбітражу й інтерфейсу системної шини; схеми арбітражу керуючої разом зі схемами арбітражу інших арбітрів пріоритетним доступом; схеми інтерфейсу системної шини, що виробляє сигнали запиту на захоплення системної шини і приймаючого сигналів підтвердження захоплення; схеми керування і синхронізації; схеми керування контролером шини й фіксаторами адреси.

Рисунок 1.3.1. - Структурна схема процесорного модуля

2. Спеціальний розділ

2.1. Вибір і обґрунтування елементної бази

Системний контролер і шинний формувач КР580ВК28.

Системний контролер і шинний формувач КР580ВК28 призначено для фіксації слова-стану МП, вироблення системних керуючих сигналів, буферизації шини даних МП і керування напрямком передачі даних.

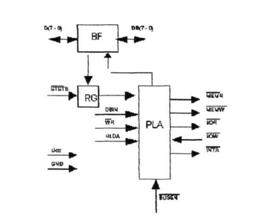

Структурна схема системного контролера і шинного формувача (СКФ) приведена на рис.2.1.1. До складу СКФ входять: шинний формувач-підсилювач (BF), що забезпечує збільшення навантажувальної здатності системної інформаційної шини; регістр (RG) для запису і збереження слова-стану МП; комбінаційна схема (PLA) для формування вихідних керуючих сигналів.

Рисунок 2.1.1. - Структурна схема системного контролера і шинного формувача (СКФ).

Призначення вхідних, вихідних, вихідних і керуючих сигналів СКФ приведені при описі виводів мікросхеми в табл.2.1.1.

Таблиця 2.1.1. - Опис виводів СКФ

| Позначення виводу | Номер контакту | Призначення виводу |

| D(7 - 0) | 8; 21; 19; 6; 10; 12; | Входи/виходи даних |

| 17; 15 | (з боку МП) | |

| STSTB | 1 | Строб стану (від ГТИ) |

| DBIN | 4 | Вхід сигналу "ПРИЙОМ" від МП |

| WR | 3 | Вхід сигналу "ВИДАЧА" від МП |

| HLDA | 2 | Вхід сигналу "ПІДТВЕРДЖЕННЯ ЗАХОПЛЕННЯ" від МП |

| DB(7 - 0) |

7; 20; 18; 5; 9; 11; 16; 13 |

Входи/виходи інформаційної системної шини |

| MEMR | 24 | Читання пам'яті |

| MEMW | 26 | Запис у пам'ять |

| I/OR | 25 | Читання з ВУ |

| I/OW | 27 | Запис у ВУ |

| BUSEN | 22 | Дозвіл роботи шин - сигнал Н-рівня, що установлює усі виходи у високоімпедансний стан |

| INTA | 23 | Підтвердження переривання - сигнал L-рівня, використову-ваний для стробування введення адреси підпрограми обслуговування переривання |

| Ucc | 28 | Напруга живлення (+5В) |

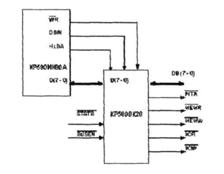

Підключення СКФ до МП наведено на рисунку 2.1.2.

Рисунок 2.1.2. - Схема підключення СКФ до МП

По сигналу STSTB, що виробляється ГТІ, відбувається запис слова-стану в регістр збереження, а потім видача його на комбінаційну схему, що формує керуючі сигнали.

Буферні регістри КР580ИР82 і КР580ИР83.

Буферні регістри КР580ИР82 і КР580ИР83 являють собою 8-розрядні паралельні регістри з тристабільними виходами. Вони використовуються для реалізації схем фіксації, буферизації і мульти-плексування в мікропроцесорних системах на базі МП КР580ИК80А та К1810ВМ86. На виходах мікросхеми КР580ИР82 генеруються не інвертовані вхідні дані, а на виходах мікросхеми КР580ИР83 - інвертовані.

Запис вхідних даних у буферні регістри виробляється при переході сигналу STB с Н-рівня в L-рівень. При Н-рівні сигналу ОЕ виходи буферних регістрів знаходяться у високоімпедансному стані.

Генератор тактових сигналів КР580ГФ24.

Мікропроцесорна інтегральна мікросхема КР580ГФ24 використовується як генератор тактових синхросерій F1 і F2 для мікропроцесора КР580ИК80А. Крім того, генератор виробляє сигнали початкової установки мікропроцесора RESET і готовності READY, які синхронізовані тактовими імпульсами, і строб STSTB, використовуваний для фіксації слова станів у системному контролері.

На рисунку 2.1.2. приведене умовне позначення генератора тактових сигналів КР580ГФ24 на електричній схемі.

Рисунок 2.1.2. - Позначення КР580ГФ24 на схемі електричній принциповій.

2.2. Принцип роботи окремих ВІС з використанням часових діаграм

В серії К580 процесор разом з пристроєм керування реалізований у вигляді окремої ВІС і має фіксовані розрядність і систему команд, "зашиту" у ВІС МП.

Схематичне зображення і позначення на електричній схемі приведене рисунку 2.2.1.

Рисунок 2.2.1. - Позначення мікропроцесора КР580ВМ80А на електричній схемі.

Функціональне призначення виводів МП КР580ВМ80А приведено в таблиці 2.2.1.

Таблиця 2.2.1. Функціональне призначення виводів МП.

| Вивід | Позначення | Тип виводу | Функціональне призначення виводів |

|

1,25- 27, 29-40 |

Аю, Ао-А2> Аз-А9ї Аі5, Ai2-A14s ^п | Виходи | Канал адреси |

| 2 | GND | - | Загальний |

| 3-10 | D4-D7, D3-D0 | Входи (виходи) | Канал даних |

| 11 | UTO | - | Напруга живлення - 5 V |

| 12 | RESET | Вхід | Установка в початковий стан |

| 13 | HOLD | Вхід | Захоплення |

| 14 | INT | Вхід | Запит переривання |

| 15,22 | Сь С2 | Входи | Тактові імпульси |

| 16 | ШТЕ | Вихід | Дозвіл переривання |

| 17 | DBIN | Вихід | Прийом інформації |

| 18 | -WR | Вихід | Видача інформації |

| 19 | SYNC | Вихід | Сигнал синхронізації |

| 20 | Ucci | - | Напруга живлення +5 V |

| 21 | HLDA | Вихід | Підтвердження захоплення |

| 23 | RDY | Вхід | Сигнал "Готовність" |

| 24 | WATT | Вихід | Сигнал "Чекання" |

| 28 | '"Цвда | - | Напруга живлення +12 V |

Цикл команд МП складається з машинних циклів, число яких для різних команд неоднакове і коливається в межах від одного до трьох. Машинний цикл потрібно кожного разу, коли ЦП звертається до пам'яті чи до порту вводу/виводу. На кожен байт обраної команди приділяється один машинний цикл, що містить три-п'ять тактів. На рис.2.2.2. показаний цикл команди з трьома звертаннями до пам'яті, що складається з трьох машинних циклів.

Рисунок 2.2.2. - Цикли і стани МП

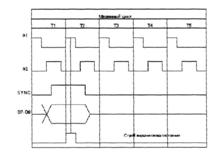

Спочатку кожного машинного циклу ЦП видає на шину даних вісім розрядів інформації, що характеризує стан внутрішніх вузлів МП. Ця інформація знаходиться на шині даних протягом дії сигналу SYNC, що завжди з'являється в першому такті будь-якого машинного циклу. Інформація про стан МП по сигналу стробу видачі слова стану записується в спеціальний зовнішній регістр стану і зберігається в ньому до появи наступного стробу, тобто протягом усього часу машинного циклу, що залишився. Строб видачі слова стану формується поза МП логічним перемножуванням сигналів Ф1 і SYNC, як показано на рисунку 2.2.3. Таким чином, шина даних протягом короткого проміжку часу використовується для видачі і запису в зовнішній регістр слова стану внутрішніх вузлів МП, в інший час – за своїм прямим призначенням.

Рисунок 2.2.3. - Видача слова стану внутрішніх вузлів МП

Здавалося б природним для видачі інформації про стан МП використовувати додаткові висновки, аналогічні тим, що використовуються для видачі сигналів WR, DBIN, SYNC і ін., однак припустиме число виводів, що підключаються до одного кристала ІМС, дуже обмежено. Штучне мультиплексування шини даних дозволяє зменшити число виводів МП.

Інформація про стан внутрішніх вузлів МП показує, які дії будуть виконуватися протягом поточного машинного циклу. Існує 10 різновидів машинних циклів і відповідних їм різних слів стану МП, приведених у табл.2.2.2, де кожен розряд слова формує відповідний сигнал. Назви і призначення цих сигналів зазначені в табл.2.2.З.

Таблиця 2.2.2. Значення розрядів слова стану МП

для різних машинних циклів.

|

№ п/п |

Тип машинного циклу | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

| 1. | Вибір команди (Мі) | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 2. | Читання з пам'яті | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 3. | Запис у пам'ять | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4. | Читання стека | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 5. | Запис у стек | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6. | Уведення | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7. | Висновок | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 8. | Підтвердження | ||||||||

| Дозволу переривання | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | |

| 9. | Підтвердження | ||||||||

| зупинки | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | |

| 10. | Підтвердження | ||||||||

| переривання зупинці | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 |

Таблиця 2.2.3. Призначення розрядів слова стану МП.

| Розряд | Позначення і найменування сигналу | Призначення розряду | ||

| D7 | MEMR | Читання з пам'яті | Вказує на те, що в даному циклі буде вироблятися читання з пам'яті | |

| D6 | ЮТ | Введения | На шинах адресу установлений номер пристрою введення. Передбачається введення інформації в ЦП | |

| D5 | Ml | Вибір першого байта | Поточний цикл служить для вибору першого байта команди | |

| D4 | OUT | Висновок | На шинах адресу установлений номер пристрою виведення. Передбачається виведення інформації при сигналі WR | |

| D3 | HLTA | Підтвердження зупинки | Відгук на команду HLT. Підтверджує зупинку | |

| D2 | STACK | Стік | На шинах адресу встановлена адреса з покажчика стека | |

| Dl | WO | Запис чи виведення | На шинах даних знаходиться інформація для запису в пам'ять чи для виведення на зовнішній пристрій | |

| DO | ШТА | Підтвердження Переривання | Стробування номера запиту на переривання при дійсному сигналі DBIN | |

Формування керуючих сигналів.

Взаємодія МП із пам'яттю і пристроями введення-виведення здійснюється по сигналах шини керування. Частина сигналів надходить на цю шину безпосередньо. Інша частина сигналів, такі як I/OR, I/OW, MEMR, MEMW, формується відповідно до інформації, збереженої в регістрі слова стану fPSWY.

2.3. Принцип роботи пристрою згідно схеми електричної принципової

Блок процесора містить у собі МП ВІС D3, генератор тактових імпульсів D2, системний контролер D6, підсилювачі MA D4 і D5, підсилювач сигналів МП ВІС D7.

Клавіша SB1 служить для подачі сигналу початкової установки МП ВІС, тривалість якого визначається ланцюгом R2, С2. Діод VD1 дозволяє здійснити швидкий розряд С2 навіть при короткочасному зникненні живлячої напруги. Ланцюг СІ, BQ1 задає частоту генератора тактових імпульсів. Набори резисторів Е1... ЕЗ служать для узгодження сигналів МА і МД. Виходи IMC D4, D5, D6 переводяться в третій стан при захопленні магістралей по сигналу КГЕК, що виробляється елементом D1. Резистор забезпечує високий рівень на вході D1 при відсутності в системі модуля з контролером ПДП, що виробляє сигнал BUSEN.

Блок запам'ятовуючих пристроїв містить ПЗП і схему дешифрації адреси. Дешифратор адреси формує сигнали вибірки CS1 для ПЗП в такому вигляді: ПЗП з 0000Н по 07FFH.

Блок дешифрації адреси ПВВ видає вісім стробіруючих імпульсів низького рівня для регістрів введення і виведення мікро-ЕОМ. Формування здійснює ПЗП D30, що дешифрує чотири молодших розряди МА і сигнал запису в ПВВ. ПЗП відмикається по сигналу з логічної схеми D27... D29. Елементом D27 схеми виконується дешифрація інших розрядів адреси, а елемент D28 служить для одержання сигналу звертання до ПВВ (читання чи запису). Для заборони роботи ПВВ мікро-ЕОМ під час циклів заборони роботи ПВВ мікро-ЕОМ під час циклів ПДП служить сигнал BUSEN. За допомогою перемикача SA4 можна також відключати ПВВ мікро-ЕОМ. Імпульс, що відмикає, для ПЗП D30 формується елементом D29 при надходженні на його входи високих рівнів. Резисторна матриця служить навантаженням виходів з відкритим колектором ПЗП, а резистори R18. R19 формують високі рівні.

3. Експлуатаційний розділ

3.1. Ініціалізація програмуємих ВІС

Програма ініціалізації мікросхем виконує налагодження портів вводу-виводу мікросхем та встановлює параметри дільника та входів мікросхеми по яким буде виконуватися переривання. Також налагоджуються переривання по таймеру. Всі інші переривання забороняються.

Програму тестування та програму ініціалізації ВІС приведено в пункті 3.2.

3.2. Тест перевірки окремих вузлів або пристрою

Тест-програма перевірки роботи модуля процесора написана мовою асемблера МП 8080.

ORG 0000Н; Початок

MVI А, 90Н; Програмування

OUT 08Н; ПШ

IN05H; Читання інф. з порту А

STA0800Н; Запис у комірку пам'яті

XRAА; Очищення А

LXIН,0800Н; Початок ОЗП

MVIА,55Н; в А 01010101

Ml: MOVМ, А; Записати в пам'ять

INXН; На наступний адресу ОЗП

MOV C, А; Зберегти А

MOVA, H; Значення Н в А

CPI1 OH; Кінець ОЗП

MOVA, C;

JNZMl; Якщо ні, йти на Ml

LXIH,0800H; Початок ОЗП

М2: CMPM;

JNZM3; Указати на помилку

INХН; Збільшити адресу

MOVС, А;

MOVА, Н;

СРІІОН; Кінець ОЗП

MOVА, С;

JNZМ2; Якщо ні, йти на М2

HLTКінець програми

Таблиця 3.2.1. - Тест-таблиця для налагодження

МП модуля в покроковому режимі.

|

№ п/п |

Адреса | Дані | MRDC | MWTC | IORC | IOWC | Команда | ||

| 1 | 0000 0001 | ЗЕ 90 | 0 0 | 1 1 | 1 16 | 1 1 | MVT А, 90Н | ||

| 2 | 0002 | 03 | 0 | ■ | |||||

| 0003 | 08 | 0 | OUT 08Н | ||||||

| 0008 | 90 | 1 | 0 | ||||||

| 3 | 0004 | 08 | 0 | ||||||

| 0005 | 05 | 0 | IN 05Н | ||||||

| 0006 | 55 | 1 | 0 | ||||||

| 4 | 0007 0008 | 33 00 | 0 0 | STA 0800Н | |||||

| 0009 | 08 |

0 1 |

0 | ||||||

| 080A | 55 | ||||||||

| 5 | 0000 | AF | 0 | XRA A | |||||

| 6 | 0001 | 21 | 0 | ||||||

| 0002 | 00 | 0 | LXI | ||||||

| 0003 | 08 | 0 | H,0800H | ||||||

| 7 | 0004 0005 | ЗЕ 55 | 0 0 | MVI A,55H | |||||

| 8 | 0006 | 77 | 0 | MOV M,A | |||||

| 0807 | 55 | 1 | 0 | ||||||

| 9 | 0007 | 23 | 0 | 1 | INX H | ||||

Хоча модуль і здається простим, наявність у ньому тісного взаємозв'язку між апаратними засобами і програмним забезпеченням приводить до того, що навіть незначна несправність у апаратурі або в програмному забезпеченні приводить до непрацездатності мікро-ЕОМ.

Почати налагодження мікро-ЕОМ доцільно з перевірки омметром усіх зв'язків на монтажній платі й усунення виявлених дефектів монтажу. З особливою старанністю варто перевірити наявність електричних зв'язків між виводами живлення мікросхем і контактами джерела живлення. Щупами омметра необхідно торкатися безпосередньо виводів мікросхем - це допоможе знайти дефекти пайки. Потім перевіряють наявність живлячої напруги на виводах мікропроцесора і на інших мікросхемах модуля.

Наступний етап - перевірка схеми формування синхроімпульсів. Для цього буде потрібно осцилограф. Переконавши в наявності синхроімпульсів Ф1 і Ф2 на виводах мікропроцесора, переходять до перевірки функціонування блоку центрального процесора при постійно діючій на шині даних команді NOP (00Н). Код команди 00 примусово подають на шину даних за допомогою перемичок.

При цьому на адресній шині повинний відбуватися послідовний перебір всіх адрес, який можна проконтролювати за допомогою осцилографа. Сигнали на адресній шині в цьому випадку мають форму симетричних прямокутних імпульсів, причому частота імпульсів зменшується вдвічі при збільшенні номера розряду на одиницю. При правильній роботі команди NOP переходять до перевірки інших блоків мікро-ЕОМ. Для цього вивід 3 мікросхеми DD2 з'єднують із загальним проводом і переконуються в наявності високого рівня на виводі 24 мікропроцесора, що свідчить про перебування його в стані очікування. Натиснувши на кнопку "УСТ" перевіряють на всіх лініях шини адреси нульового рівня, а на лініях шини даних двійкового коду 0011 1110, записаного в нульовому осередку (мікросхема ПЗП).

Вставляють у панельку мікросхему ПЗП. Збирають на окремій платі вузол, за допомогою якого перевіряють поциклове виконання тест-програми мікропроцесором. При однократному натисканні на кнопку "КРОК" мікропроцесор переходить у стан очікування, що дозволяє на індикаторах логічного пробника контролювати читання з ПЗП кодів і їх виконання.

Для виключення впливу сигналу переривання провід від виводу 14 мікропроцесора DD1 відключають.

Натиснувши на кнопку "УСТ" і послідовно натискаючи кнопку "КРОК", контролюють виконання перших команд Тест-програми відповідно до Тест-таблиці 3.2.1

При виявленні невідповідностей варто перевірити чи нема замикання між лініями шини адреси, або шини даних, або іншими сигнальними лініями.

Після усунення виявлених несправностей, домігшись виконання перших команд тесту в кроковому режимі, додатковий вузол відключають.

3.3. Розрахунок надійності пристрою

Надійність – властивість пристрою виконувати задані функції в заданих режимах і умовах застосування, обслуговування, ремонту, збереження, транспортування на протязі необхідного інтервалу часу.

Показники надійності:

Безвідмовність.

Довговічність.

Ремонтопридатність.

Збереження.

Безвідмовність – властивість безупинно зберігати працездатність до граничного стану, після настання, якого подальша експлуатація виробу економічно недоцільна.

Ремонтопридатність – пристосованість пристрою до попередження відмовлень, до можливості виявлення та усунення несправностей шляхом проведення ремонту і технічного обслуговування.

До термінів ремонтопридатності відносяться: відмовлення, збереження.

Відмовлення – подія, що полягає в повній або частковій утраті працездатності пристрою.

Відмовлення бувають:

Раптові (катастрофічні) – стрибкоподібна зміна параметрів робочого виробу.

Поступові (параметричні) – постійна зміна одного або декількох параметрів з часом, що виходять за припустимі межі.

Збереження – термін, протягом якого при дотриманні режимів збереження виріб зберігає працездатний стан.

Розрахунок надійності поділяється на три розділи:

Визначення значення інтенсивності відмовлення всіх елементів за принциповою схемою вузла пристрою.

Визначення значення імовірності безвідмовної роботи всієї схеми.

Визначення середнього наробітку до першого відмовлення.

Виконання розрахунків проходить наступним чином:

1. Інтенсивність відмовлення всіх елементів визначається за формулою:

![]() (3.3.1)

(3.3.1)

де:

ni – кількість елементів у схемі;

li – інтенсивність відмовлень і-го елемента;

m – кількість типів елементів.

При розрахунку також потрібно враховувати інтенсивність відмовлень через пайки радіоелементів на друкованій платі.

Інтенсивність відмовлень елементів розраховуємо за формулою:

![]() (3.3.2)

(3.3.2)

де:

lо – інтенсивність відмовлень елементів у режимі номінального навантаження;

Кe – експлуатаційний коефіцієнт;

Кр – коефіцієнт навантаження.

Усі ці параметри беруться з довідника з розрахунку надійності.

2. Ймовірністю безвідмовної роботи називається ймовірність того, що за певних умов експлуатації в заданому інтервалі часу не відбудеться жодного відмовлення.

Ймовірність безвідмовної роботи визначається за формулою:

![]() (3.3.3)

(3.3.3)

де:

![]() -

інтенсивність відмов всіх елементів;

-

інтенсивність відмов всіх елементів;

t – час, (год).

За результатами розрахунків складається таблиця і графік.

3. Середній наробіток до першого відмовлення – це час роботи пристрою до першої відмови.

Середній наробіток на відмовлення визначається за формулою:

![]() (3.3.4)

(3.3.4)

Розрахунок надійності пристрою приведено далі.

Анотація

В курсовому проекті розроблена схема електрична принципова процесорного модуля з використанням мікропроцесора КР580ВМ80А. В роботі використана велика кількість схем, що дозволяють розглянути кожну частину пристрою окремо, а також програма перевірки процесорного модуля, що дає можливість перевірити правильність роботи процесорного модуля. В роботі представлено розрахунок надійності пристрою.

Виконання даної курсової роботи змусило повторити та закріпити вивчений протягом навчального року матеріал з предмету "Мікропроцесорні системи", а також звернутися до додаткової літератури та вивчити багато нового.

Література

1. Методичні вказівки щодо виконання курсової роботи.

2. Аналоговые и цифровые интегральные микросхемы / Под ред. С.В. Якубовского. - М. Радио и связь, 1984.

3. Бороволоков Э.П. Фролов В.В. "Радиолюбительские схемы" // К.: Кондор – 1995 – 6 с.

4. Балашев Е.П., Григорьев В.Л., Петров Г.А. Микро - и мини-ЭВМ. - Л.: Энергоатомииздат, 1984.

5. А.С. Басманов "МП и ОЭВМ", Москва, "Мир", 1988.

6. Алексеенко А.Г., Галицын А.Д., Иванников А.Д. Проектирование радиоэлектронной литературы на микропроцессорах. - М.: Радио и связь, 1984.

7. Якименко Ю.І., Терещенко Т.О., Сокол Є.І. Мікропроцесорна техніка. 2004.

8. Вершинин О.Е. Применение микропроцессоров для автоматизации технологических процессов. - Л. Энергоатомииздат, 1986.