Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Реферат: Виды триггеров

Реферат: Виды триггеров

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

КАФЕДРА РЭС

РЕФЕРАТ

НА ТЕМУ:

«Виды триггеров»

МИНСК, 2009

Триггеры вида [F] , как и триггеры вида [L], относятся к разряду устройств, у которых прием и фиксация информации совмещены во времени. Такие триггеры могут быть синхронными и асинхронными.

Наиболее широкое распространение в интегральной схемотехнике получили синхронные триггеры RS-, D- и JK-типов.

В триггерах вида [F] для записи информации используется не весь сигнал, а только его фронт. Такие триггеры имеют следующий алгоритм работы. В отсутствие переключающего фронта ТИ информация на логических входах может принимать любые комбинации. При этом состояние на выходах триггера не изменяется. При поступлении фронта ТИ осуществляется запоминание информации внутренней памятью схемы управления и ее фиксация на выходах триггера. Одновременно схема управления вырабатывает сигнал блокировки (его длительность равна длительности ТИ), который блокирует прием информации, и она не воспринимается входными цепями в течение всей последующей длительности ТИ.

Блокировка входов может быть полной или частичной (последняя только у тактируемых триггеров). Тактируемые триггеры с полной блокировкой входов характеризуются тем, что при поступлении фронта ТИ осуществляется запрет на прием информации для любых комбинаций входных сигналов, включая нейтральную т. е. ту, при которой осуществляется режим ее хранения (для RS-триггера это комбинация R=S=0). В триггерах с неполной блокировкой входов возможны комбинации входных сигналов, при которых сигнал блокировки не вырабатывается. В результате при таких комбинациях триггеры реагируют на смену информации не только во время действия фронта ТИ, но и во время действия его уровня.

Триггеры, срабатывающие

по фронту 01 и 10, обозначают индексами ![]() и

и

![]() , если они обладают полной

блокировкой входов, и индексами

, если они обладают полной

блокировкой входов, и индексами ![]() и

и ![]() , если таковой не обладают.

Примеры индексной записи триггеров:

, если таковой не обладают.

Примеры индексной записи триггеров: ![]()

![]() ,

, ![]() ,

, ![]() ,

, ![]() и т. д.

и т. д.

Триггеры с управлением записью вида [F] имеют более сложную схему по сравнению с триггерами вида [L], но обладают более высокой помехоустойчивостью, поскольку сигнал помехи в такие триггеры может записываться только в очень короткий интервал времени, практически совпадающий с длительностью фронта, тогда как в триггерах вида [L] помеха может приниматься триггером в течение всей длительности сигнала ТИ.

Триггер ![]() -типа

-типа

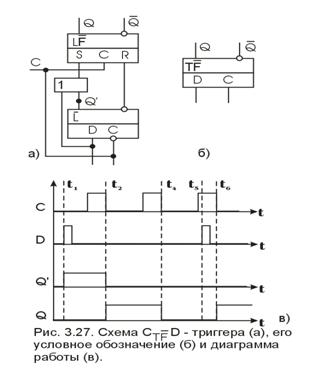

Триггер ![]() -типа получил широкое

применение в интегральной схемотехнике. Схема триггера, ее обозначение и

временная диаграмма работы представлены на рис. 1.

-типа получил широкое

применение в интегральной схемотехнике. Схема триггера, ее обозначение и

временная диаграмма работы представлены на рис. 1.

Предположим, что триггер находится в состоянии Q=0, а на входе D уровень логической 1 (D=1). В этом случае имеет место следующее распределение потенциалов на выходах вентилей схемы управления триггера: В1=В2=В3=1, В4=0. В результате только вентиль В2 оказывается подготовленным к переключению, так как на одном из его входов присутствует уровень 1 с выхода вентиля В1. При поступлении ТИ на вход С на выходе элемента В2 сформируется сигнал с уровнем 0, под действием которого триггер установится в состояние Q=1. Одновременно сигнал с выхода вентиля В2, поступая на входы вентилей В1 и В3, принудительно удерживает их в состоянии 1 в течение всей длительности ТИ, и тем самым смена информации на входе D не отразится на состоянии триггера. Это достаточно наглядно иллюстрируется временной диаграммой (рис. 1, в).

|

В момент t3 произошла смена информации на входе D с 1 на 0. Однако триггер остался в

состоянии Q=1. В момент t4 на вход D

поступил сигнал помехи, но и в этом случае триггер не изменил своего состояния.

Триггер установится в состояние 0 (Q=0) в момент t5, поскольку к моменту поступления фронта

ТИ на входе D действовал уровень 0 (D=0). И опять смена информации на

входе D с 0 на 1 в момент t6 не отразится на выходе триггера, поскольку сигнал

блокировки теперь уже снимаемый с выхода В3 (В3=0), будет

удерживать вентиль В4 в состоянии 1 (В4=1). Таким

образом, триггер работает в соответствии с уравнением Qn+1=Dn и является ![]() -триггером. Важной особенностью

работы триггера является то, что при смене уровня ТИ, то есть при его

тактировании сигналами с уровнем логического 0, он также будет фиксировать

информацию по фронту F. Такой

режим называют работой с внутренней задержкой, поскольку информация на

выходе триггера появляется после окончания ТИ.

-триггером. Важной особенностью

работы триггера является то, что при смене уровня ТИ, то есть при его

тактировании сигналами с уровнем логического 0, он также будет фиксировать

информацию по фронту F. Такой

режим называют работой с внутренней задержкой, поскольку информация на

выходе триггера появляется после окончания ТИ.

Триггеры, обладающие

свойством работать в режиме с внутренней задержкой, обозначаются индексом t (Dt, RSt, Tt, JKt и др.). Этим индексом удобно

пользоваться, когда важен сам факт работы триггера в режиме с внутренней

задержкой, а не способы управления записью видов F, LF и другие,

позволяющие проектировать триггеры с внутренней задержкой. Другими словами,

индекс t характеризует одно общее свойство

триггеров с различными видами управления записью, а именно возможность фиксации

информации после окончания тактирующего или информационного сигнала. Таким

образом, например, запись ![]() означает,

что триггер RS-типа может быть выполнен с одним из

видов управления

означает,

что триггер RS-типа может быть выполнен с одним из

видов управления ![]() ,

, ![]() ,

, ![]() и др. (в данном случае неважно

каким) и фиксирует информацию после окончания ТИ (аналогично CtD, CtJK и т. д.).

и др. (в данном случае неважно

каким) и фиксирует информацию после окончания ТИ (аналогично CtD, CtJK и т. д.).

В асинхронных триггерах режим с внутренней задержкой также характеризуется индексом t, например, записи (R-S)t, Rt-St означают, что по входам R и S информация на выходах фиксируется после окончания информационного сигнала без учета того, каким образом это осуществляется в схемотехническом плане (аналогично Tt, Jt-Kt→(J-K)t).

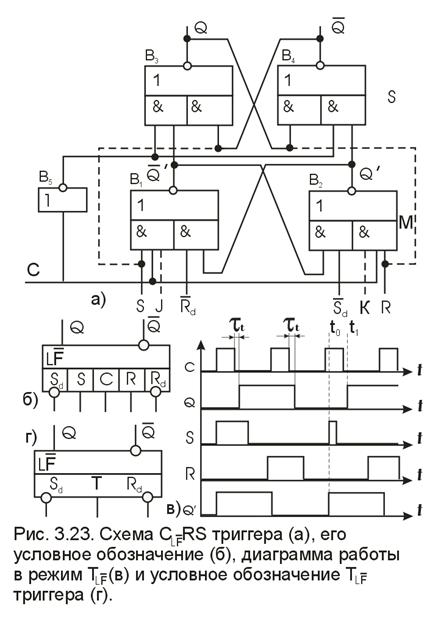

CRS-триггер с управлением записью вида F

Схема такого триггера представлена на рис. 2.

|

Предположим, что триггер находится в состоянии 1 (Q=1), а на его входах действует комбинация сигналов S=0, R=1. В этом случае имеет место следующее распределение потенциалов на выходах вентилей В1-В4: В4=0, В1-В3=1. В результате вентиль В2 окажется подготовленным к переключению, так как на двух его входах из трех действует уровень 1. При поступлении ТИ (момент t1 на диаграмме рис. 2, в) на выходе вентиля В2 сформируется сигнал с уровнем 0, под действием которого триггер установится в состояние Q=0, и одновременно этот сигнал с выхода В2 будет удерживать вентили В1 и В3 в состоянии 1, запрещая тем самым прием информации в схему управления.

Это означает, что с

момента появления сигнала на выходе вентиля В2 информация на входах R и S триггера может принимать любые значения (моменты ![]() ), но это изменение не

будет влиять на состояние триггера в целом, то есть он останется в состоянии Q=0. В момент t5 сигнал с уровнем 0 теперь уже сформируется на выходе вентиля

В3, так как к моменту поступления фронта F очередного ТИ именно этот вентиль будет подготовлен к

переключению. В результате триггер установится в состояние Q=1 и будет запрещен прием информации

в схему управления, то есть триггер останется в состоянии Q=1, хотя на его входах информация

будет изменятся (момент t6, t7).

), но это изменение не

будет влиять на состояние триггера в целом, то есть он останется в состоянии Q=0. В момент t5 сигнал с уровнем 0 теперь уже сформируется на выходе вентиля

В3, так как к моменту поступления фронта F очередного ТИ именно этот вентиль будет подготовлен к

переключению. В результате триггер установится в состояние Q=1 и будет запрещен прием информации

в схему управления, то есть триггер останется в состоянии Q=1, хотя на его входах информация

будет изменятся (момент t6, t7).

В момент t8 приходит сигнал помехи по входу R, но триггер не срабатывает, так как

отсутствует ТИ на входе С. В момент t9 снова

сформируется сигнал на выходе вентиля В3 и триггер подтвердит свое

единичное состояние. К моменту t10 на входах R и S

будет действовать уровень 0 и по логике работы триггера F он не должен реагировать на смену

информации на его входах после прихода фронта F. В момент t11, как видно из диаграммы, на вход R поступает сигнал помехи, но тем не

менее триггер устанавливается в состояние Q=0, хотя входной сигнал поступил после прихода фронта ТИ. Последнее

означает, что данный триггер является триггером CfRS-типа, так как не обладает полной блокировкой

входов, поскольку существует одна комбинация входных сигналов S=R=0, при которой триггер реагирует на смену информации на его

входах после поступления фронта ТИ. Следует отметить, что данный триггер, как и

триггер ![]() -типа, может работать от

сигналов ТИ с уровнем логического 0, то есть в режиме с внутренней задержкой (CtRS-триггер).

-типа, может работать от

сигналов ТИ с уровнем логического 0, то есть в режиме с внутренней задержкой (CtRS-триггер).

Кроме рассмотренных

триггеров в интегральной схемотехнике широко применяются и другие типы

триггеров такие как ![]() и

и ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() типов и другие, то есть с

прямым и инверсным управлением по информационным входам.

типов и другие, то есть с

прямым и инверсным управлением по информационным входам.

Следует иметь ввиду, что триггеры вида F должны фиксировать на своих выходах только ту информацию, которая действует на его входах в момент поступления фронта ТИ. А это означает, что триггеры не должны запоминать информацию, действующую на его входах при отсутствии ТИ. Применительно к любому функциональному типу триггера сказанное означает, что в отсутствие ТИ информация на его входах может изменяться по любому закону, и если к моменту поступления фронта ТИ на его входах окажется нейтральная комбинация сигналов, при которой триггер находится в режиме хранения (для JK-триггера это J=K=0), то с поступлением фронта ТИ, триггер должен подтвердить свое состояние, то есть остаться в состоянии Qn.

Кроме тактируемых,

находят применение и асинхронные триггеры, срабатываемые по фронту. Среди них

наиболее широко используются триггеры ![]() и

и

![]() типов, то есть триггеры с

одним информационным входом, срабатываемые по фронту 01 и 10 соответственно.

типов, то есть триггеры с

одним информационным входом, срабатываемые по фронту 01 и 10 соответственно.

Триггер Т-типа, или счетный триггер, под действием каждого входного сигнала переключается в инверсное состояние, то есть функционизирует в соответствии с уравнением:

![]() .

.

Триггеры Т-типа находят

исключительно широкое применение, поэтому всегда стараются их проектировать с

минимальным числом вентилей. Применительно к элементам типа И-НЕ, ИЛИ-НЕ,

наиболее экономичными по числу вентилей являются триггеры ![]() и

и ![]() типов, построенные на

основе

типов, построенные на

основе ![]() и

и ![]() триггеров.

триггеров.

Триггеры, в которых прием и фиксация информации разнесены во времени

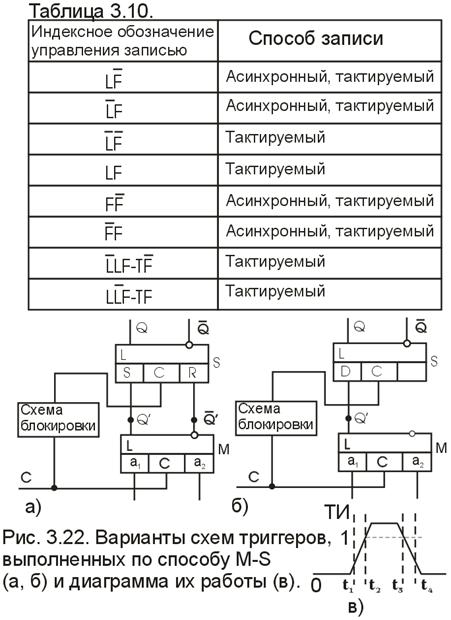

К рассматриваемым триггерам относятся триггеры, у которых для приема и фиксации информации используются как минимум два фрагмента сигнала. Такими фрагментами сигнала могут быть уровень и фронт нарастания, уровень и срез, фронт и срез. Возможные виды триггеров, различаемых по способам управления записью, индексное обозначение которых включает только прописные буквы приведены в таблице 1.

В составе рассматриваемых триггеров встречаются также триггеры, индексная запись которых содержит и строчные буквы аналогично триггерам вида f. В итоге число триггеров, различаемых по способам управления будет значительно больше, чем указано в табл. 1.

Триггеры с

управлением записью вида![]()

Такие триггеры работают

по следующему алгоритму: принимают информацию схемой управления по

уровню сигнала аналогично триггерам вида L с одновременным ее запоминанием, а на выходах фиксируют по

фронту ![]()

![]() информационного

или тактирующего сигнала. Поскольку триггеры принимают информацию по уровню, а

фиксируют по фронту, то смена информации на его входах отразится и на его

выходах, но после окончания переключающего фронта.

информационного

или тактирующего сигнала. Поскольку триггеры принимают информацию по уровню, а

фиксируют по фронту, то смена информации на его входах отразится и на его

выходах, но после окончания переключающего фронта.

Находят применение и триггеры,

в которых нарушается приведенный алгоритм работы при некоторых комбинациях

входных сигналов. В таких триггерах при смене информации в ходе записи она

может зафиксироваться на входах еще до поступления фронта ![]() , что должно учитываться

при конкретном применении триггера. Такие триггеры будем называть триггерами с

неполной блокировкой выходов и обозначать индексом

, что должно учитываться

при конкретном применении триггера. Такие триггеры будем называть триггерами с

неполной блокировкой выходов и обозначать индексом ![]() .

.

|

Триггеры с управлением

записью вида ![]() применяются при проектировании

счетчиков, сдвигающих регистров и относятся к разряду наиболее широко

распространенных устройств, выпускаемых промышленностью в интегральном

исполнении.

применяются при проектировании

счетчиков, сдвигающих регистров и относятся к разряду наиболее широко

распространенных устройств, выпускаемых промышленностью в интегральном

исполнении.

В схемотехническом плане рассматриваемые триггеры выполняются по способу Master-Slave (сокращенно M-S). В соответствии с этим способом триггеры реализуются на двух тактируемых триггерах — основном М и вспомогательном S по схеме, показанной на рис. 3, где в качестве основных всегда используются триггеры требуемого функционального типа, а в качестве вспомогательных — триггеры CLRS- или CLD-типа.

В практике проектирования триггерных устройств встречается большое многообразие схемотехнических вариантов их построения, которые отличаются лишь организацией узла блокировки. Очевидно, что такое многообразие триггеров, выполненных одним и тем же способом, требует введения дополнительной классификации, присваивающей определенное название триггеру. Названия триггерам даются по схемному решению узла блокировки. Например, если узел блокировки выполняется на одном инверторе, то триггер будет называться M-S-триггером с блокирующим инвертором.

Кроме M-S-триггеров с блокирующим инвертором широко применяются следующие разновидности триггеров:

· M-S-триггеры с двумя блокирующими инверторами;

· M-S-триггеры с внутренними запрещающими связями;

· M-S-триггеры с разнополярным тактированием;

· M-S-триггеры с коммутирующими транзисторами.

Возможны и другие схемотехнические решения узла блокировки. Однако все они имеют одну и ту же цель — разрешить передачу информации из триггера М в триггер S во время отсутствия ТИ и запретить, то есть блокировать передачу состояния триггера М в триггер S при действии ТИ. При этом для надежной работы устройства необходимо, чтобы процесс записи и блокировки передачи информации между триггерами происходил в последовательности, показанной на рис. 3, в:

1. в момент t1 осуществляется запрет (блокировка) на передачу информации из триггера M в триггер S;

2. в момент t2 разрешается запись информации в триггер M;

3. в момент t3 осуществляется запрет на прием информации в триггер M;

4. в момент t4 разрешается передача состояния из триггера М в триггер S.

Другими словами, для

надежности работы триггера необходимо опережающее действие блокировки над

процессом записи информации. Каждый из перечисленных выше M-S-триггеров, построенных тем или иным схемотехническим

приемом, имеет определенные преимущества перед другими, а такие триггеры как ![]() ,

, ![]() ,

, ![]() ,

, ![]() типов являются основными

триггерами цифровых систем.

типов являются основными

триггерами цифровых систем.

M-S-триггеры с блокирующим инвертором

Особенность построения

таких устройств заключается в том, что в тактовую цепь между основным и

вспомогательным триггерами включается инвертор, обеспечивающий блокировку

передачи состояния триггера M в

триггер S во время действия ТИ. Принцип работы

рассмотрим на примере ![]() триггера,

выполненного на элементах И-ИЛИ-НЕ (рис. 4).

триггера,

выполненного на элементах И-ИЛИ-НЕ (рис. 4).

В исходном положении (ТИ=0) основной и вспомогательный триггеры находятся в одинаковом состоянии, поскольку на выходе элемента В5 действует уровень 1, разрешающий передачу информации из триггера М в S. Допустим, что начальное состояние триггера соответствует 0 (Q=0), а на его входы поданы сигналы S=1 и R=0. При поступлении тактирующего сигнала (С=1) основной триггер по входу S установится в состояние 1 (Q`=1), а вспомогательный за счет действия уровня 0 на выходе инвертора В5 останется в начальном состоянии 0 (Q=0). После окончания ТИ (С=0) на выходе инвертора В5 сформируется уровень 1 и вспомогательный триггер примет состояние основного.

|

|

С учетом задержки

инвертора информация на выходах ![]() и

и ![]() сформируется через

интервал времени

сформируется через

интервал времени ![]() после окончания

ТИ, то есть τt

— это задержка формирования информации на выходах триггера

после окончания

ТИ, то есть τt

— это задержка формирования информации на выходах триггера ![]() и

и ![]() . Чтобы установить

. Чтобы установить ![]() триггер в 0 (Q=0), на его входы необходимо подать

комбинацию сигналов S=0 и R=1. Одновременная подача сигналов S=R=1 во время действия ТИ для триггера (рис. 4) недопустима,

поскольку триггер устанавливается в неопределенное состояние после окончания

ТИ. Для такого составного триггерного устройства (СТУ), как и для простых

тактируемых триггеров, необходимо учитывать, что смена информации на входах

будет фиксироваться триггером М и, следовательно, после окончания ТИ отразится

и на выходах вспомогательного триггера (на рис. 4,в в момент t0 на вход S поступил сигнал помехи и в момент t1 эта помеха зафиксировалась на выходе триггера).

триггер в 0 (Q=0), на его входы необходимо подать

комбинацию сигналов S=0 и R=1. Одновременная подача сигналов S=R=1 во время действия ТИ для триггера (рис. 4) недопустима,

поскольку триггер устанавливается в неопределенное состояние после окончания

ТИ. Для такого составного триггерного устройства (СТУ), как и для простых

тактируемых триггеров, необходимо учитывать, что смена информации на входах

будет фиксироваться триггером М и, следовательно, после окончания ТИ отразится

и на выходах вспомогательного триггера (на рис. 4,в в момент t0 на вход S поступил сигнал помехи и в момент t1 эта помеха зафиксировалась на выходе триггера).

В схеме триггера на рис. 4,а возможны состязания, что является одним из недостатков такой организации блокировки. В данном случае элемент В5 состязается с элементами И-ИЛИ-НЕ основного триггера.

Наличие состязаний

является следствием невыполнения пункта 1) — условий надежной работы М-S триггера («в момент t1 осуществляется запрет (блокировка) на передачу

информации из триггера М в триггер S»). Следовательно, чтобы убедиться в функциональной надежности триггера,

надо выяснить при каких условиях состязания становятся опасными. Поскольку переключение

триггера М из состояния 0 (Q=0) в

1(Q=1) и наоборот всегда осуществляется через

переходное состояние ![]() =

=![]() =0, то схема триггера (рис.

4, а) будет функционально надежна, если выполняется условие

=0, то схема триггера (рис.

4, а) будет функционально надежна, если выполняется условие

![]() ,

,

где ![]() — средняя минимальная

задержка переключения элементов И-ИЛИ-НЕ триггера М. Иначе говоря, уровень 0 на

выходе блокирующего инвертора должен сформироваться раньше, чем триггер М

переключиться в инверсное состояние. В противном случае во время действия ТИ может

произойти смена состояния во вспомогательном триггере S, что недопустимо, так как устройство должно работать в

режиме

— средняя минимальная

задержка переключения элементов И-ИЛИ-НЕ триггера М. Иначе говоря, уровень 0 на

выходе блокирующего инвертора должен сформироваться раньше, чем триггер М

переключиться в инверсное состояние. В противном случае во время действия ТИ может

произойти смена состояния во вспомогательном триггере S, что недопустимо, так как устройство должно работать в

режиме ![]() триггера. Пользуясь

понятием относительной длины состязающих цепей ∆, можно записать, что RS-триггер будет функционально надежен,

если

триггера. Пользуясь

понятием относительной длины состязающих цепей ∆, можно записать, что RS-триггер будет функционально надежен,

если ![]() .

.

При наличии в составе ИМС группы элементов, отличающихся различным быстродействием, для которых известны значения величин τmax и τmin, выполнение данного условия не представляет каких-либо трудностей. Но если значения задержек элементов неизвестны, схему триггера на рис. 4, а желательно не применять.

Важной особенностью ![]() триггеров, выполненных по

способу М-S, является то, что они могут быть

легко преобразованы в другие типы триггеров, в частности

триггеров, выполненных по

способу М-S, является то, что они могут быть

легко преобразованы в другие типы триггеров, в частности ![]() ,

, ![]() типов.

типов.

Преобразование ![]() триггера в счетный триггер

(его обозначение показано на рис. 4,г) осуществляется коммутацией выходов

триггера в счетный триггер

(его обозначение показано на рис. 4,г) осуществляется коммутацией выходов ![]() и

и ![]()

![]() триггера к его входам R и S соответственно (на рис. 4,а эта коммутация показана

штриховыми линиями).

триггера к его входам R и S соответственно (на рис. 4,а эта коммутация показана

штриховыми линиями).

Для получения ![]() триггера достаточно к T-триггеру, полученному на основе

триггера достаточно к T-триггеру, полученному на основе ![]() триггера, добавить два

информационных входа J и K, как это показано на рис. 4, а

штриховыми линиями. Если в этом триггере объединить входы J и K и на этот объединенный вход подать сигнал с уровнем 1, то он

будет работать в режиме счетного триггера.

триггера, добавить два

информационных входа J и K, как это показано на рис. 4, а

штриховыми линиями. Если в этом триггере объединить входы J и K и на этот объединенный вход подать сигнал с уровнем 1, то он

будет работать в режиме счетного триггера.

Общим недостатком триггеров, построенных по способу M-S с блокирующим инвертором, следует считать наличие явлений состязаний.

К достоинствам таких триггеров можно отнести небольшое число элементов (при выполнении триггеров на элементах И-ИЛИ-НЕ) и, как следствие этого, достаточно высокое быстродействие и малое число переключаемых за период элементов.

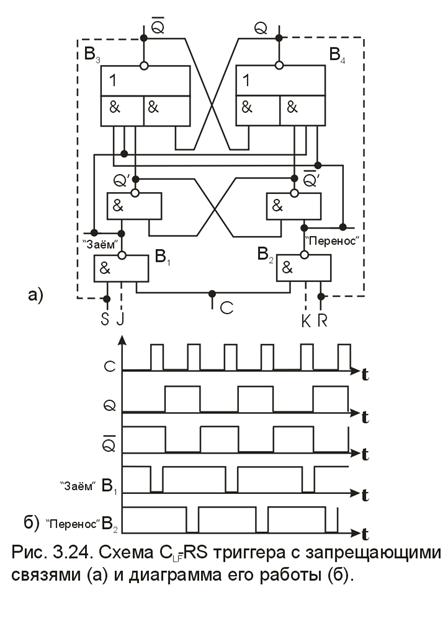

М-S-триггеры с запрещающими связями

Блокировка передачи состояния из триггера М в триггер S во время действия ТИ в данных триггерах осуществляется за счет дополнительных блокирующих связей с выходов вентилей триггера М. Принцип работы таких устройств рассмотрим на примере триггера, схема которого приведена на рис. 5.

В отсутствие ТИ (С=0) на выходах вентилей В1 и В2 уровни 1 и, следовательно, разрешается передача состояния из триггера М в S. При поступлении ТИ (С=1) на выходах вентилей В1 (при S=1 и R=0) или В2 (при S=0 и R=1) формируется уровень 0, запрещающий передачу состояния М в S и устанавливающий триггер М в состояние 1 (Q`=0) или 0 (Q`=0).

По окончании ТИ (С=0),

наоборот, сначала запрещается прием кода в триггер М (так как ТИ=0) и только

затем, то есть после формирования уровня 1 на выходах вентилей В1 и

В2, разрешается передача состояния триггера М в триггер S. Таким образом выполняются условия

надежной работы и тем самым гарантируется функциональная надежность устройства.

Однако оно имеет одну важную особенность, которую необходимо учитывать в

процессе его применения, заключающуюся в том, что если во время действия ТИ

информация на одном из входов с единичного управляющего уровня сменяется на

нулевой, то на выходах вентилей В2 и В1 сформируется

разрешающий сигнал и информация из триггера М перепишется в триггер S. Другими словами, смена информации

на входах триггера приводит к нарушению алгоритма работы, так как информация на

выходах триггера появляется не после окончания ТИ, а во время его действия, то

есть не осуществляется блокировка выходов во время действия ТИ. Рассмотренная

схема является схемой триггера с неполной блокировкой выходов, то есть является

триггером ![]() -типа. Организация

триггеров

-типа. Организация

триггеров ![]() и

и ![]() типов, построенных на базе

типов, построенных на базе ![]() триггера, показана на рис.

5 штриховыми линиями.

триггера, показана на рис.

5 штриховыми линиями.

|

Важной особенностью этой схемы является то, что в режиме Т-триггера она формирует сигналы «Перенос» и «Заем» (рис. 5, б).

Другой особенностью М-S-триггера является то, что он может

работать в качестве асинхронных триггеров ![]() и

и

![]() типов. Это достигается

подачей на тактовый вход С уровня 1.

типов. Это достигается

подачей на тактовый вход С уровня 1.

М-S-триггеры с разнополярным тактованиием

Особенностью построения триггеров является то, что основной и вспомогательный триггеры тактируются взаимно инверсными сигналами. Этим обеспечивается надежная блокировка передачи информации в триггер S в момент ее записи в основной, чем и гарантируется высокая функциональная надежность.

Триггер, выполненный по данной схеме, представлен на рис. 6.

|

Здесь основной и

вспомогательный триггеры реализованы на элементах И-ИЛИ-НЕ, причем основной

является ![]() -триггером, а вспомогательный

-триггером, а вспомогательный

![]() триггером. В отсутствие ТИ

(С=0) закрыты вентили И1, И2 элемента В3 или В4

и состояние триггера М постоянно переписывается в триггер S. Так, если триггер М находится в

состоянии

триггером. В отсутствие ТИ

(С=0) закрыты вентили И1, И2 элемента В3 или В4

и состояние триггера М постоянно переписывается в триггер S. Так, если триггер М находится в

состоянии ![]() `=0,

`=0, ![]() `=1, то будут закрыты вентили

И1 и И2 элемента В4, то есть на его выходе

уровень 1 и, следовательно, триггер S в этом случае находится в состоянии

`=1, то будут закрыты вентили

И1 и И2 элемента В4, то есть на его выходе

уровень 1 и, следовательно, триггер S в этом случае находится в состоянии ![]() =0,

=0,

![]() =1. При поступлении ТИ

(С=1) откроется вентиль И1 элемента В3, то есть триггер S запомнит состояние триггера М.

Одновременно с процессом хранения информации вспомогательным триггером

происходит запись информации в триггер М. Однако информация, записываемая в

триггер М во время действия ТИ, не воспринимается триггером S, поскольку уровень 0 на выходе

=1. При поступлении ТИ

(С=1) откроется вентиль И1 элемента В3, то есть триггер S запомнит состояние триггера М.

Одновременно с процессом хранения информации вспомогательным триггером

происходит запись информации в триггер М. Однако информация, записываемая в

триггер М во время действия ТИ, не воспринимается триггером S, поскольку уровень 0 на выходе ![]() удерживает в закрытом

состоянии вентили И1, И2 элемента В4, то есть

осуществляется запрет приема информации триггером S. По окончании ТИ запрет снимается (С=0) и осуществляется

прием информации триггером S,

который в переходный период проходит через состояние

удерживает в закрытом

состоянии вентили И1, И2 элемента В4, то есть

осуществляется запрет приема информации триггером S. По окончании ТИ запрет снимается (С=0) и осуществляется

прием информации триггером S,

который в переходный период проходит через состояние ![]() =

=![]() =1.

=1.

Этот триггер, как и все

рассмотренные ранее, может быть легко преобразован в триггер ![]() и

и ![]() типов (на рис. 6 показано

штриховыми линиями).

типов (на рис. 6 показано

штриховыми линиями).

Данный триггер обладает минимальным числом элементов и максимальным быстродействием, что является преимуществом перед ранее рассмотренными триггерами. Однако наряду с максимальным быстродействием имеет минимальное значение параметра nQ (нагрузочная способность триггера по выходу) и максимальное значение параметра nc (эквивалент нагрузки триггера по тактовому входу), что ограничивает его эксплуатационные возможности при проектировании более сложных цифровых узлов. Рассматриваемый триггер также не может быть преобразован в асинхронный, что снижает его функциональные возможности. Однако благодаря высокому быстродействию и малому числу элементов он находит достаточно широкое применение.

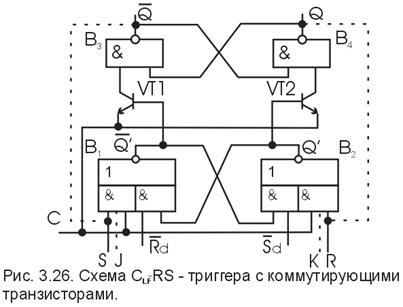

М-S-триггеры с блокирующими транзисторами

В таких триггерах организация блокировки передачи информации из триггера М в триггер S во время действия ТИ осуществляется за счет дополнительных блокирующих транзисторов, включенных между основным и вспомогательным триггерами. Схемная реализация такого триггера приведена на рис. 7.

|

В отсутствие ТИ (С=0)

открыт один из двух блокирующих транзисторов VT1 или VT2 и притом тот, на базе которого

действует уровень 1. Предположим, что триггер М находится в состоянии ![]() `=1,

`=1, ![]() `=0. В этом случае открыт

транзистор VT2, то есть на его коллекторе низкий уровень и,

следовательно, на выходе элемента В4 действует уровень 1 (

`=0. В этом случае открыт

транзистор VT2, то есть на его коллекторе низкий уровень и,

следовательно, на выходе элемента В4 действует уровень 1 (![]() =1), а на выходе В3

— уровень 0 (

=1), а на выходе В3

— уровень 0 (![]() =0). При поступлении ТИ

(С=1) оба транзистора оказываются закрытыми высоким уровнем сигнала,

действующим на их эмиттерах, и тем самым обеспечивается сохранность информации

триггером S и блокировка приема информации от

триггера М, в который в это же время производится запись информации. По окончании

ТИ (С=0) блокировка снимается, то есть на эмиттерных входах обоих транзисторов

действуют уровни 0 и осуществляется передача состояния триггера М в триггер S. При этом триггер S устанавливается в новое состояние

через переходное состояние

=0). При поступлении ТИ

(С=1) оба транзистора оказываются закрытыми высоким уровнем сигнала,

действующим на их эмиттерах, и тем самым обеспечивается сохранность информации

триггером S и блокировка приема информации от

триггера М, в который в это же время производится запись информации. По окончании

ТИ (С=0) блокировка снимается, то есть на эмиттерных входах обоих транзисторов

действуют уровни 0 и осуществляется передача состояния триггера М в триггер S. При этом триггер S устанавливается в новое состояние

через переходное состояние ![]() =

=![]() =1.

=1.

Организация ![]() и

и ![]() триггеров на базе данного

триггера показана на рис. 7 штриховыми линиями.

триггеров на базе данного

триггера показана на рис. 7 штриховыми линиями.

Резюме: кроме рассмотренных, возможны и другие схемотехнические приемы организации блокировки в М-S-триггерах. Однако приведенные схемные решения получили наибольшее распространение в силу их высоких схемотехнических и функциональных возможностей.

Из других разновидностей триггеров с различными способами управления записью рассмотрим

Триггеры с

управлением записью видов ![]() ,

, ![]()

Данные триггеры

существуют только в тактируемом варианте и работают по следующему алгоритму: в

отсутствие и во время действия ТИ информация принимается и запоминается

внутренней памятью схемы управления. Другими словами, такие триггеры принимают

информацию в течение всей длительности периода, а фиксируют по срезу ТИ. В

дальнейшем эти триггеры будем называть триггерами вида ![]() , где Т — период следования

ТИ. Возможны два варианта таких триггеров

, где Т — период следования

ТИ. Возможны два варианта таких триггеров ![]() и

и

![]() . Особенности их работы

рассмотрим на примере

. Особенности их работы

рассмотрим на примере ![]() триггера, схема

которого приведена на рис. 8.

триггера, схема

которого приведена на рис. 8.

|

Она включает в себя

триггеры ![]() ,

, ![]() и элемент ИЛИ. Работа

триггера иллюстрируется диаграммой (рис. 8, в). В момент t1 на вход D поступает сигнал с уровнем 1, и так как

и элемент ИЛИ. Работа

триггера иллюстрируется диаграммой (рис. 8, в). В момент t1 на вход D поступает сигнал с уровнем 1, и так как ![]() триггер

принимает информацию по уровню

триггер

принимает информацию по уровню ![]() , то в

момент t1 триггер установится в состояние

, то в

момент t1 триггер установится в состояние ![]() `=1. После окончания ТИ

(момент t2) состояние Q=1 зафиксируется и на выходе триггера. Одновременно в момент t2 на входе D установится уровень 0 и

`=1. После окончания ТИ

(момент t2) состояние Q=1 зафиксируется и на выходе триггера. Одновременно в момент t2 на входе D установится уровень 0 и ![]() триггер

примет нулевое состояние (Q`=0).

триггер

примет нулевое состояние (Q`=0).

К некоторому моменту t3 ![]() триггер

будет находиться в состоянии 0 и, следовательно, в момент t4 это состояние зафиксируется и на выходе

триггер

будет находиться в состоянии 0 и, следовательно, в момент t4 это состояние зафиксируется и на выходе ![]() триггера (Q=0). В момент t5 вновь поступает сигнал D=1. Но теперь

триггера (Q=0). В момент t5 вновь поступает сигнал D=1. Но теперь ![]() триггер

не принимает эту информацию. В итоге состояние D=1 через элемент ИЛИ поступает на вход S

триггер

не принимает эту информацию. В итоге состояние D=1 через элемент ИЛИ поступает на вход S ![]() триггера и фиксируется на его выходах после окончания

ТИ (момент t6).

триггера и фиксируется на его выходах после окончания

ТИ (момент t6).

В интегральной

схемотехнике применяются в основном ![]() триггеры,

хотя в практике возможны и другие их функциональные типы, например

триггеры,

хотя в практике возможны и другие их функциональные типы, например ![]() триггеры.

триггеры.

ЛИТЕРАТУРА

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. М.: Мир, 2001. - 379 с.

2. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.: ИНТУИТ.РУ, 2003. - 440 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.: Политехника, 2006. - 885 с.

4. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш. шк., 2001. - 526 с.

5. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. М.: Радио и связь, 2000. - 416 с.

6. Соломатин Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. - 160 с.