Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Рефераты по косметологии

Рефераты по криминалистике

Рефераты по криминологии

Рефераты по науке и технике

Рефераты по кулинарии

Рефераты по культурологии

Курсовая работа: Микропроцессорная система на базе комплекта КР580

Курсовая работа: Микропроцессорная система на базе комплекта КР580

Федеральное агентство образования Российской Федерации

Государственное образовательное учреждение

среднего профессионального образования

Краснотурьинский индустриальный колледж

Специальность: Вычислительные машины, комплексы, системы и сети

Курсовой проект по предмету микропроцессоры и микросистемы

на тему: Микропроцессорная система на базе комплекта КР580

Краснотурьинск 2009

Содержание

Введение

1. Описание применяемых элементов

1.1 Микропроцессор КР580ВМ8

1.2 Генератор тактовых импульсов КР580ГФ2

1.3 Контроллер прерываний КР580ВН5

1.4 Системный контроллер КР580ВК28

1.5 Программируемый последовательный интерфейс КР580ВВ51

1.6 Контроллер клавиатуры и дисплея КР580ВВ79

1.7 Микросхема ОЗУ К537РУ17

1.8 Микросхема ПЗУ К573РФ6

1.9 Микросхема дешифратора К155ИД3

1.10 Микросхема К514ИД2

1.11 Буферный регистр 1533АП5

2. Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

2.2 Построение схем дешифрации адресов памяти

2.3 Расчет и планирование адресного для устройств ввода-вывода

2.4 Построение схем дешифрации адресов устройств ввода-вывода

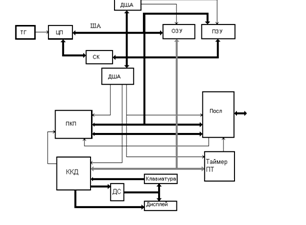

3. Структурная схема

4. Принципиальная схема

Заключение

Список используемой литературы

Введение

В данном курсовом проекте рассмотрен микропроцессорный комплект серии КР580. Этот набор микросхем, аналогичен набору микросхем Intel 82xx. Представляет собой 8-разрядный комплект на основе n-МОП технологии. Система команд СМ1800, ГОСТ 11305.910-80. Большинство микросхем является аналогами чипов серии MCS-85 фирмы Intel.

В настоящее время для построения различных микропроцессорных систем, устройств обработки информации и различных устройств вычислительной техники широко используются микропроцессорные системы на базе серии КР580.

В комплект КР580 входит:

- Микропроцессор КР580ВМ80;

- Системный контроллер КР580ВК28;

- Параллельный интерфейс КР580ВВ55;

- Контроллер прерываний КР580ВМ59;

- Контроллер клавиатуры и дисплея КР580ВВ79.

Хотя этот микропроцессорный комплект был создан в восьмидесятых годах, он широко используется до сих пор и изучается в различных образовательных заведениях так как, изучив его, можно понять работу более сложных микропроцессорных систем.

Микропроцессор КР580 используется в различных системах с не высокими требованиями к производительности, и в тех системах, когда использование более мощных процессоров экономически не выгоден.

Данный курсовой проект необходим, для того чтобы учащиеся изучили основные элементы микропроцессорного комплекта, поняли их работу, научились самостоятельно строить микропроцессорные системы, научились находить неполадки и устранять их.

1. Описание используемых элементов

1.1 Микропроцессор кр580вм80

Процессор содержит 4500 транзисторов по технологии 6 мкм n-МДП Тактовая частота процессора КР580ВМ80 - 2 МГц. Каждая команда выполняется за 1..5 машинных циклов, каждый из которых состоит из 3..5 тактов. Средняя производительность 200..300 тыс. операций в секунду на частоте 2 МГц. Микропроцессор имеет раздельные 16-разрядную шину адреса и 8-разрядную шину данных. 16-разрядная шина адреса обеспечивает прямую адресацию внешней памяти объемом до 64 Кбайт и 256 устройств ввода/вывода.

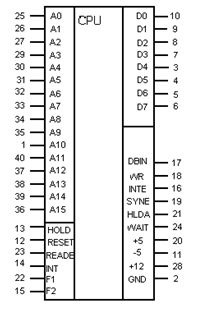

Рисунок 1. Условное обозначение микросхемы КР580ВМ80

Таблица 1.Назначение выводов микропроцессора КР580ВМ80

| Вывод | Обозначение | Назначение выводов |

| 6,5,4,3,7,8,9,10 | D0-7 | Двунаправленная шина данных |

|

25,26,27,29,30,31,32,33,34,35, 1,40,37,38,39,36 |

А0-15 | Шина адреса |

| 15,22 | F1, F2 | Тактовые сигналы |

| 13 | HOLD | Запрос захвата шин |

| 14 | INT | Запрос прерывания |

| 23 | READY | Готовность |

| 12 | RESET | Сигнал системного сброса |

| 16 | INTE | Разрешение прерывания |

| 17 | DBIN | Ввод с шины данных |

| 18 | WR | Запись |

| 19 | SYNC | Сигнал синхронизации |

| 21 | HLDA | Подтверждение захвата шин |

| 24 | WAIT | Ожидание или подтверждение состояния ожидания |

| 11 | -5V | -5В |

| 20 | +5V | +5В |

| 28 | + 12V | + 12В |

| 2 | GND | Общий |

1.2 Генератор тактовых импульсов КР580ГФ24

Микросхема КР580ГФ24 - генератор тактовых сигналов фаз С1, С2, предназначен для синхронизации работы микропроцессора КР580ВМ80.

Генератор формирует:

- две фазы С1, С2с положительными импульсами, сдвинутыми во времени, амплитудой 12В и частотой 0,5 - 3,0МГц;

- стробирующий сигнал составляет STB длительностью не менее (Топ/9-15нс), где Топ - период тактовых сигналов опорной частоты;

- тактовые сигналы. С, синхронные с фазой С2, амплитудой уровня ТТЛ.

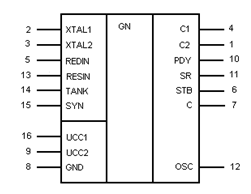

Рисунок 2. Условное обозначение микросхемы КР580ГФ24

Таблица 2. Назначение выводов генератора тактовых импульсов КР580ГФ24

| Вывод | Обозначение | Назначение выводов |

| 1 | SR | Установки в исходное состояние микропроцессора и системы |

| 2 | RESIN | Установка 0 |

| 3 | RDYIN | Сигнал "Готовность" |

| 4 | RDY | Сигнал "Готовность" |

| 5 | SYN | Сигнал синхронизации |

| 6 | C | Тактовый сигнал, синхронный с фазой С2 |

| 7 | STB | Стробирующий сигнал состояния |

| 8 | GND | Общий |

| 9 | Ucc2 | Напряжение питания +12В |

| 10 | C2 | Тактовые сигналы -фазы С2 |

| 11 | C1 | Тактовые сигналы -фазы С1 |

| 12 | OSC | Тактовые сигналы опорной частоты |

| 13 | TANK | Вывод для подключения колебательного контура |

| 14, 15 | XTAL1, XTAL2 | Выходы для подключения резонатора |

| 16 | Ucc1 | Напряжение питания +5В |

1.3 Системный контроллер КР580ВК28

Микросхема КР580ВК28 - системный контролер, применяется в микропроцессорных системах на базе микропроцессора КР580ВМ80 для формирования управляющих сигналов.

Системный контролер формирует управляющие сигналы по сигналам состояния микропроцессора при обращении к ЗУ: RD и WR, при обращении к УВВ: RDI0 и WRI0, INTA, а также обеспечивает прием и передачу 8-разрядной информации между каналом данных микропроцессора.

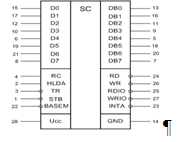

Рисунок 3. Условное обозначение микросхемы КР580ВК28

Таблица 3. Назначение выводов системного контроллера КР580ВК28

| Вывод | Обозначение | Назначение выводов |

| 1 | STB | Стробирующий сигнал состояния |

| 2 | HLDA | Подтверждение захвата |

| 3 | TR | Выдача информации |

| 4 | RC | Прием информации |

| 5, 7, 9, 11, 13, 16, 18, 20 | DB4, DB7, DB3, DB2, DB0, DB1, DB5, DB6 | Канал данных системы |

| 6, 8, 10, 12, 15, 17, 19, 21 | D4, D7, D3, D2, D0, D1, D5, D6 | Канал данных микропроцессора |

| 14 | GND | Общий |

| 22 | BUSEN | Управление передачей данных и выдачи сигналов |

| 23 | INTA | Подтверждение запроса прерывания |

| 24 | RD | Чтение из ЗУ |

| 25 | RDI0 | Чтение из УВВ |

| 26 | WR | Запись в ЗУ |

| 27 | WRI0 | Запись в УВВ |

| 28 | Ucc | Напряжение питания +5В |

1.4 Контроллеры интерфейса RS 232

1.4.1 Микросхема КР580ВВ51

Микросхема КР580ВВ51-универсальна синхронный приемопередатчик, предназначен для аппаратной реализации последовательного протокола обмена между микропроцессором КР580ВМ80 и каналами последовательной передачи дискретной информации.

Микросхема преобразует параллельный код, получаемый от центрального процессора, в последовательный поток символов со служебными битами и выдает этот поток в последовательный канал связи с различной скоростью, а также выполняет обратное преобразование: последовательный поток символов в параллельный 8-разрядное слово.

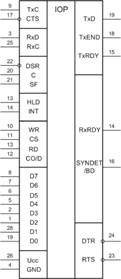

Рисунок 4.1. Условное обозначение микросхемы КР580ВВ51

Таблица 4. Назначение выводов микросхемы КР580ВВ51

| Вывод | Обозначение | Назначение вывода |

| 1, 2, 5-8, 27, 28 | D2-D7, D0, D1 | Канал данных - обмен информацией между микропроцессором и микросхемой |

| 3 | RxD | Приемник микросхемы |

| 4 | GND | Общий |

| 9 | TxC | Синхронизации передачи |

| 10 | WR | Запись информации |

| 11 | CS | Выбор микросхемы |

| 12 | CO/D | Управление (данные) |

| 13 | RD | Чтение информации |

| 14 | RxRDY | Готовность приемника |

| 15 | TxRDY | Готовность передатчика |

| 16 | SYNDET/BD | Двунаправленный трех - стабильный программируемый ввод/вывод |

| 17 | CTS | Готовность внешнего устройства принять данные |

| 18 | TxEND | Конец передачи |

| 19 | TxD | Передатчик микросхемы |

| 20 | C | Синхронизация |

| 21 | SR | Установка исходного состояния |

| 22 | DSR | Готовность внешнего устройства передать данные |

| 23 | RTS | Запрос приемника внешнего устройства на прием данных |

| 24 | DTR | Запрос передатчика внешнего устройства на прием данных |

| 25 | RxC | Синхронизация приема |

| 26 | Ucc | Напряжение питания +5В |

Таблица 4.1. Таблица истинности сигналов микросхемы КР580ВВ51

| Сигналы на входах | Направление и вид информации | |||

| СО/D | RD | WR | CS | |

| 1 | 1 | 0 | 0 | Канал данных системы управление |

| 0 | 1 | 0 | 0 | Канал данных системы данных |

| 1 | 0 | 1 | 0 | Канал данных системы состояния |

| 0 | 0 | 1 | 0 | Канал данных системы данных |

| Х | 1 | 1 | 0 | Высокоомныое состояние канала данных |

| Х | Х | Х | 1 | |

1.4.2 Таймер КР580ВИ53

Микросхема КР580ВИ53 -трехканальное программируемое устройство (таймер), предназначено для организации работы микропроцессорных систем в режиме реального времени. Программируемый таймер реализован в виде трех независимых 16-разрядных каналов с общей схемой управления. Каждый канал может работать в шести режимах.

Управляющее слово определяет режим работы канала, тип счета, формат чисел.

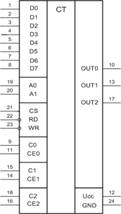

Рисунок 4.2. Условное обозначение микросхемы КР580ВИ53

Таблица 4.3. Назначение выводов микросхемы КР580ВИ53

| Вывод | Обозначение | Назначение выводов |

| 1-8 | D7-D0 | Канал данных |

| 9, 15, 18 | C0, C1, C2 | Синхронизация каналов 0-2 |

| 10, 13, 17 | OUT0, OUT1, OUT2 | Сигналы каналов 0, 1, 2 |

| 11, 14, 16 | CE0, CE1, CE2 | Сигналы каналов 0, 1, 2 |

| 12 | GND | Общий |

| 19, 20 | A0, A1 | Сигналы выбора каналов 0, 1, 2 |

| 21 | CS | Выбор микросхемы |

| 22 | RD | Чтение |

| 23 | WR | Запись |

| 24 | Ucc | Напряжение питания 5В |

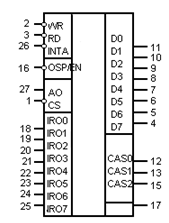

1.5 Контроллер прерываний КР580ВН59

Предназначен для организации обработки приоритетных 8-уровневых запросов прерываний от восьми внешних устройств. Контроллер КР580ВН59 был разработан для микропроцессорных систем, построенных только на основе микропроцессора КР580ВМ80. Контроллеры прерываний можно каскадировать для получения 64-уровневой системы прерываний.

Рисунок 5. Условное обозначение микросхемы КР580ВН59

Таблица 5. Назначение выводов КР580ВН59

| Вывод | Обозначение | Назначение выводов |

| 11,10,9,8,7,6,5,4 | D0-7 | Шина данных микропроцессора |

| 3,2 | RD/WR | Чтение/запись информации в регистры |

| 27 | А0 | Разряд шины адреса микропроцессора |

| 1 | CS | Сигнал выбора кристалла |

|

18,19,20,21,22, 23,24,25 |

IR0-7 | Сигналы запросов прерываний от внешних устройств ввода/вывода |

| 17 | INT | Сигнал запроса прерываний, поступающий на микропроцессор |

| 26 | INTA | Сигнал подтверждения прерывания, поступающий от микропроцессора |

| 16 | SP/EN | Программирование ведомого/разрешения буфера |

| 12,13,15 | CAS0-2 | Линии каскадирования |

| 14 | GND | Общий |

| 28 | Vcc | Питание |

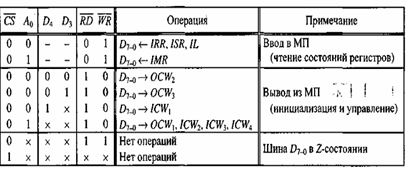

Таблица 5.1. Таблица истинности

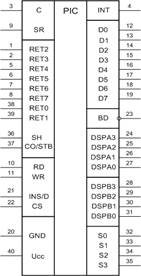

1.6 Контроллер клавиатуры и дисплея КР580ВВ79

Программируемое интерфейсное устройство, предназначенное для ввода и вывода информации в системах, выполненных на основе 8- и 16-разрядного микропроцессора КР580ВМ80. Кроме того, микросхема может применяться и как самостоятельное устройство при выполнении требований, предъявляемых к электрическим и временным параметрам.

Клавиатурная часть обеспечивает ввод информации в микросхему через линии возврата RET7-RET0 с клавиатуры (клавиатурная матрица объемом 8 слов*8 разрядов с возможностью расширения до 4*8 слов*8 разрядов) и матрицы датчиков (8 слов*8 разрядов), а также ввод по стробирующему сигналу (8 слов*8 разрядов). Для хранения информации в микросхеме предусмотрено 8 байт ОЗУ.

Дисплейная часть микросхемы обеспечивает вывод информации по 4-разрядным каналам DSPA3-DSPA0 и DSPB3-DSPB0 в виде двоичного кода на 8- и 16-разрядные цифровые или алфавитно-цифровые дисплеи.

Рисунок 6. Условное обозначение микросхемы КР580ВВ79

Таблица 6. Назначение выводов микросхемы КР580ВВ79

| Вывод | Обозначение | Назначение выводов |

| 1, 2, 5-8, 38, 39 | RET2-RET7, RET0, RET1 | Линии возврата |

| 3 | C | Синхронизация |

| 4 | INT | Запрос прерывания |

| 9 | SR | Установка |

| 10 | RD | Чтение информации |

| 11 | WR | Запись информации |

| 1-19 | D0-D7 | Канал данных |

| 20 | GND | Общий |

| 21 | INS/D | Команда / данные |

| 22 | CS | Выбор микросхемы |

| 23 | BD | Гашение отображения |

| 24-27 | DSPA3-DSPA0 | Канал дисплея А |

| 28-31 | DSPB3-DSPB0 | Канал дисплея В |

| 32-35 | S0-S3 | Линии сканирования |

| 36 | SH | Сдвиг |

| 37 | CO/STB | Управление / стробирующий сигнал |

| 40 | Ucc | Напряжение сигнала |

1.7 Микросхема ОЗУ К537РУ17

Статическое асинхронное ОЗУ на основе КМОП-структур.

По заданию ОЗУ нам необходимо 8 кбайт. Следовательно, нам необходимо поставить 1 штуку.

Классификационные параметры К537РУ17:

· Информационная емкость – 64 Кбит = 8 Кбайт

· Организация - 8К*8

· Время выборки адреса - не более 200 нс.

· Выход - три состояния

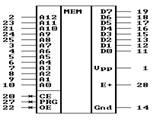

Рисунок 7. Условное обозначение микросхемы К537РУ17

Таблица 7. Назначение выводов микросхемы К537РУ17

| Выводы | Назначение | Обозначение |

|

2,3-10, 21,23,24,25 |

Адресные входы |

А12,А7-А0 А10,А11,А9,А8 |

|

11-13, 15-19 |

Входы-выходы данных |

DO0-DO2, DO3-DO7 |

| 20,26 | Выбор микросхемы |

-CE1,CE2 |

| 22 | Разрешение по выходу | -OE |

| 27 | Сигнал записи - считывания | -WE |

| 28 | Напряжение питания |

Ucc |

| 1 | Свободный | --- |

| 14 | Общий | 0 В |

Таблица 7.1. Таблица истинности микросхемы К537РУ17

| CE1 | CE2 | -OE | WE | A0-A12 | DO0-DO7 | Режим работы |

| M | M | X | X | X | Roff | Хранение |

| L | H | X | L | A | L | Запись 0 |

| L | H | X | L | A | H | Запись 1 |

| L | H | L | H | A | Данные в прямом коде | Считывание |

| L | H | H | H | A | Roff | Запрет выхода |

Примечание: М - Любая комбинация уровней или сигналов, отличная от - CE1=L, CE2=H.

1.8 Микросхема ПЗУ К573РФ6

По заданию 48 кбайт – не обходимо 6 штук.

Для стирания записанной информации микросхему нужно извлечь из контактного устройства, замкнуть все ее выводы полоской фольги и поместить под источник УФ освещения, обеспечив ее обдув. Однако стирание можно произвести , не извлекая микросхему из контактного устройства, но тогда нужно отключить напряжение питания и сигналы. Типовые источники стирающего излучения - дуговые ртутные лампы и лампы с парами ртути в кварцевых баллонах: ДРТ-220, ДБ-8 и др. Излучение проникает к кристаллу РПЗУ через прозрачное окно в крышке корпуса. Время стирания 30...60 минут.

Для предохранения от случайного стирания информации окно в крышке корпуса закрывается специальной пленкой.

Рисунок 8. Условное обозначение микросхемы К573РФ6

Таблица 8. Назначение выводов микросхемы К573РФ6

| Выводы | Назначение | Обозначение |

| 2-10, 21,23,24,25 | Адресные входы |

А0 – A12 |

|

11-13, 15-19 |

Входы-выходы данных |

DO0-DO2, DO3-DO7 |

| 20,26 | Выбор микросхемы | -CE0,CE1 |

| 22 | Разрешение по выходу | -OE |

| 27 | Сигнал записи - считывания | -WE |

| 28 | Напряжение питания | E+ |

| 1 | Свободный | --- |

| 14 | Общий | Gnd |

Таблица 8.1. Таблица истинности К573РФ6

| A | CE | OE | РК | Upр | Ucc | |

| Хранение | X | Uн | X | X | E+ | +5В |

| Считывание | А | 1Л | 1Л | Ш | E+ | +5В |

| Контроль записи | А | 1Л | 1Л | Ш | + 19В | +5В |

| Запись слова | А | Ш | Ш | Ш | +19В | +5В |

1.9 Микросхема дешифратора К155ИД3

К155ИД3- дешифратор, позволяющий преобразовать четырехразрядный код, поступающий на входы А0-А3 в напряжение низкого логического уровня, появляющееся на одном из шестнадцати выходов 0-15. Дешифратор имеет два входа разрешения дешифрации Е0 и Е1. Эти входы можно использовать как логические, когда дешифратор ИД3 служит демультиплексором данных. Тогда входы А0-А3, используются как адресные, чтобы направить поток данных, принимаемых входами Е0 или Е1, на один из выходов 0-15. На второй, не используемый в этом включении вход Е, следует подать напряжение низкого уровня.

По входам Е0 и Е1 даются сигналы разрешения выходов, чтобы устранять текущие выбросы, которыми сопровождается дешифрация кодов, появляющихся не строго синхронно (например, поступающих от счетчика пульсаций). Чтобы разрешить прохождение данных на выходы, на входы Е0 и Е1 следует дать напряжение низкого уровня. Эти входы необходимы также при наращивании числа разрядов дешифрируемого кода. Когда на входах Е0 и Е1 присутствуют напряжения высокого уровня, на выходах 0-15 появляются высокие уровни.

Выбор контроллера по конкретному адресу осуществляется с помощью дешифратора К155ИД3 (рис. 9). Назначение его выводов показано в таблице 15.

Рисунок 9. Дешифратор К155ИД3

Таблица 9. Назначение выводов БИС К155ИД3

|

№ вывода |

Назначение |

№ вывода |

Назначение |

| 1 | Выход 0 | 13 | Выход 11 |

| 2 | Выход 1 | 14 | Выход 12 |

| 3 | Выход 2 | 15 | Выход 13 |

| 4 | Выход 3 | 16 | Выход 14 |

| 5 | Выход 4 | 17 | Выход 15 |

| 6 | Выход 5 | 18 | Вход стробирующий |

| 7 | Выход 6 | 19 | Вход стробирующий |

| 8 | Выход 7 | 20 | Вход информационный |

| 9 | Выход 8 | 21 | Вход информационный |

| 10 | Выход 9 | 22 | Вход информационный |

| 11 | Выход 10 | 23 | Вход информационный |

| 12 | Общий | 24 | Ucc |

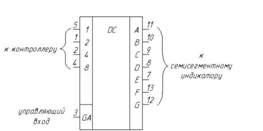

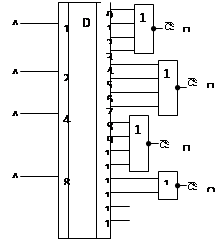

Дисплей построен на основе 8-разрядного 7-сегментоного индикатора с общим анодом CD8-BW30R6-A11, красного свечения. Для курсового проекта необходим один такой индикатор. Управление этими индикаторами осуществляет микросхема К514ИД2 (рис. 10.).

Рисунок. 10. Условное графическое обозначение дешифратора К514ИД2

Для экономии выводов микроконтроллера, а так же для удобства написания программы по выводу числовых значений на семисегментных индикаторы, в устройстве применяются дешифраторы двоичного кода в код семисегментных индикаторов. В качестве преобразователей двоичного кода в семиэлементный промышленность выпускает дешифраторы К514ИД1, К514ИД2, КР514ИД1, КР514ИД2. Для совместной работы с индикаторами, имеющими общий анод – АЛС333Б, возьмём микросхему КР514ИД2. В соответствии с рисунком 10, часть выводов подсоединяется к контроллеру, по которым на дешифратор поступает число в двоичном код, а другая часть выводов идёт на семисегментный индикатор. Так же есть вывод управления дешифратором. При подаче на этот вход логической “1”, дешифратор включён, то есть данные переводятся из двоичного кода в код семисегментных индикаторов. Если подать логический “0”, то дешифратор выключен. Максимальный выходной ток этого дешифратора составляет 25 мА. Его отличительной особенностью является то, что резисторы, ограничивающие ток, в нём отсутствуют.

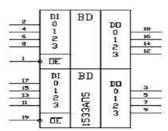

1.11 Буферный регистр 1533АП5

Для увеличения нагрузочной способности шины адреса микропроцессора и согласования этих шин с памятью и внешними устройствами необходимы шинные формирователи. В этой МПС в качестве шинного формирователя шины адреса используются буферные регистры 1533АП5 (рис. 11.). Шина адреса имеет 16 разрядов, так как этот регистр имеет 8 разрядов, для построения буфера потребуется 2 микросхемы. Одна микросхема формирует буфер для разрядов шины адреса А0-А7, а другая — А8-А15. Назначение выводов приводится в таблице 16.

Рисунок. 11. Условное обозначение буферного регистра 1533АП5 с нумерацией выводов

Таблица 11. Назначение выводов БИС 1533АП5

|

Выводы |

Назначение |

Обозначение |

|

| 2, 4, 6, 8, 17, 15, 13, 11 | Информационные входы. Подкл. к выходам микропроцессора А0-А7 для первой БИС и А8-А15 — для второй БИС | DI0-DI3 | |

| 2, 3-10, 21, 23, 24, 25, 26, 27 | Информационные выходы. Подключаются к соответствующим разрядам внешней шины | DO0-DO3 | |

| 1, 19 | Входной сигнал “Разрешение выхода”. Если OE=0, то информационные выходы перекл. в высокоимпедансное состояние | OE | |

2. Расчетная часть

2.1 Расчет и планирование адресного пространства памяти

По заданию необходима ПЗУ объемом 48 кбайт, взята микросхема объемом на 8 кбайт, следовательно, необходимо поставить таких 6 микросхем.

По заданию ОЗУ необходимо 8 кбайт. Взята микросхема объемом 8 кбайт.

Так как микропроцессор начинает выполнять программы с адреса 0 (после включения или сброса), то по этому начиная с адреса 0 должна быть, установлена ПЗУ, в которую записывается программа для начала работы устройства. В оставшейся части адресов памяти располагается ОЗУ.

Таблица 12. Расположение микросхем памяти по адресам

| Адрес | Тип памяти |

|

0000h 1FFFh |

ПЗУ1 |

|

2000h 3FFFh |

ПЗУ2 |

|

4000h 5FFFh |

ПЗУ3 |

|

6000h 7FFFh |

ПЗУ4 |

|

8000h 9FFFh |

ПЗУ5 |

|

A000h BFFFh |

ПЗУ6 |

|

C000h DFFFh |

ОЗУ |

|

E000h FFFFh |

Устройством не используется |

Следующим этапом следует расчет и построение дешифрации адресов .

Таблица 13. Расчет адресов памяти

|

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

| ПЗУ1 | 0000h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1FFFh | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ2 | 2000h | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3FFFh | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ3 | 4000h | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 5FFFh | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ4 | 6000h | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7FFFh | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ5 | 8000h | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9FFFh | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ПЗУ6 | А000h | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| BFFFh | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

| ОЗУ | C000h | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| DFFFh | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | |

|

Нет устр-в |

E000h | ||||||||||||||||

| FFFFh |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

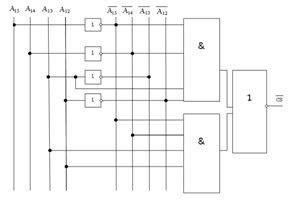

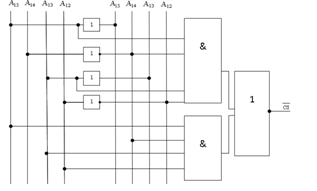

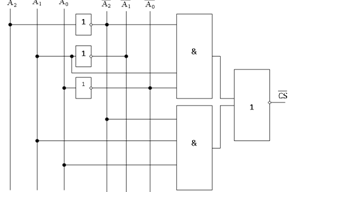

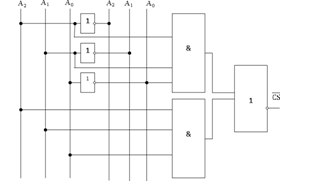

2.2 Построение схем дешифрации адресов памяти

![]()

Схема 1. Построение функции для ПЗУ

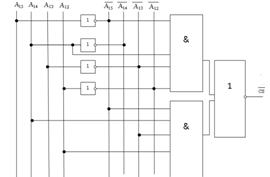

![]()

Схема 2. Построение функции для ПЗУ 2

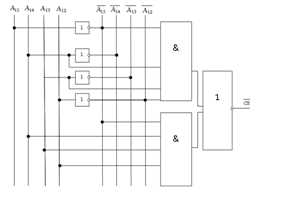

![]()

Схема 3. Построение функции для ПЗУ

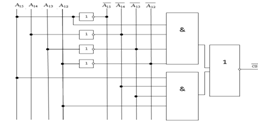

![]()

Схема 3. Построение функции для ПЗУ 4

![]()

Схема 5. Построение функции для ПЗУ 1

![]()

Схема 6. Построение функции для ПЗУ 1

![]()

Схема 7. Построение функции для ОЗУ 1

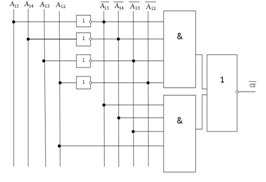

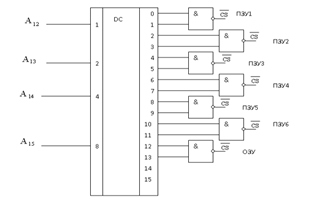

В качестве анализа четырех старших разрядов шины адреса можно использовать дешифратор двоично-десятичный, который получив двоичный код на входе активирует выход с соответствующим номером. Выходы дешифратора для каждой микросхемы объединяем функцией И.

Схема 8. Построение с помощью дешифратора

2.3 Расчет и планирование адресного для устройств ввода-вывода.

Для устройств ввода-вывода планирование адресов выполняется аналогично.

Таблица 14. Расположение микросхем устройств ввода-вывода по адресам.

|

00h 03h |

ВН59 |

|

04h 05h |

ВИ53 |

|

06h 07h |

ВВ51 |

|

08h 09h |

ВВ79 |

|

AFh FFh |

Не используется |

Следующим этапом следует расчет и построение дешифрации адресов устройств ввода-вывода.

Таблица 15. Расчет адресов памяти

|

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

||

| ВН59 | 00h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 01h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |

| ВИ53 | 02h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 03h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |

| ВВ51 | 04h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 05h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | |

| ВВ79 | 06h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 07h | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | |

| Не исп. | 08h | ||||||||||||||||

| FFh |

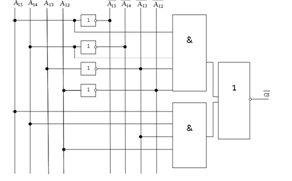

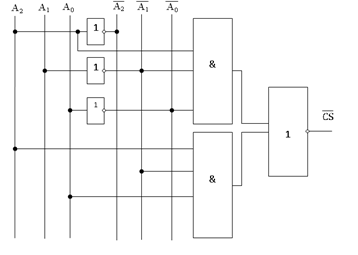

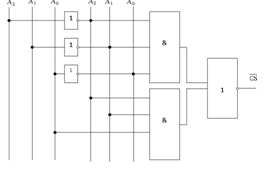

2.4 Построение схем дешифрации адресов устройств ввода-вывода

![]()

Схема 8. Построение функции для ВВ51

![]()

Схема 9. Построение функции для ВИ53

![]()

Схема 10. Построение функции для ВН59

![]()

Схема 11. Построение функции для ВВ79

В качестве анализа четырех старших разрядов шины адреса можно использовать дешифратор двоично-десятичный, который получив двоичный код на входе активирует выход с соответствующим номером.

Выходы дешифратора для каждой микросхемы объединяем функцией И.

Схема 12. Построение с помощью дешифратора.

3. Структурная схема.

Таблица 16. Перечень элементов структурной схемы

|

№ п/п |

Обозначение |

Тип элемента |

Тип микросхемы |

| 1 | ТГ | Генератор тактовых импульсов | КР580ГФ24 |

| 2 | ЦП | Центральный процессор | КР580ВМ80 |

| 3 | ДША | Дешифратор адреса | |

| 4 | ОЗУ | Оперативное запоминающее устройство | К537РУ17 |

| 5 | ПЗУ | Постоянное запоминающее устройство | К573РФ6 |

| 6 | СК | Системный контроллер | КР580ВК28 |

| 7 | ПКП | Программируемый контроллер прерывания | КР580ВН59 |

| 8 | ПИ | Программируемый последовательный интерфейс | КР580ВВ51 |

| 9 | ТП | Таймер | КР580ВН53 |

| 10 | ККД | Контроллер клавиатуры и дисплея | КР580ВВ79 |

| 11 | ДС | Схема управления дисплеем | К514ИД2 |

Структурная схема определяет основной состав изделия, его назначение и взаимосвязь.

Тактовый генератор (ТГ) формирует сигнал системного сброса RESET для установки ЦП и других устройств в начальное состояние, а так же импульсы для синхронизации работы устройств. Своими сигналами генератора тактовых импульсов обеспечивает требуемую последовательность работы всех устройств микропроцессорной системы.

Микропроцессор формирует адресную шину ША мультиплексированную шину данных ШД с шиной управления ШУ. Для увеличения нагрузочной способности шины адреса используется буферный регистр.

Демультиплексирование осуществляет системный контроллер СК, формируя на своих выходах шину данных ШД и управляющие сигналы.

Выборку микросхем памяти ОЗУ и ПЗУ, в зависимости от состояния адресных линий ША, осуществляет дешифратор ДС.

Микропроцессорная система содержит контроллер последовательного интерфейса, передатчики и приемники, которые синхронизируются независимо друг от друга сигналами от интервального таймера ПТ. Контроллер последовательного интерфейса занимает две линии прерывания, которые обслуживают контроллер прерываний ПКП.

При поступлении прерывания контроллер ПКП формирует сигнал микропроцессору, а тот в свою очередь, если прерывания разрешены, формирует сигнал.

Функции ввода с клавиатуры и отображения информации на индикаторах обеспечивает контроллер ККД.

Таблица 17. Состав принципиальной схемы.

| № | Микросхема | Обозначение на схеме |

| 1 | КР580ВМ80 | DD1 |

| 2 | КР580ГФ24 | DD2 |

| 3 | К1533АП5 | DD3, DD4 |

| 4 | КР580ВК28 | DD5 |

| 5 | К573РФ5 | DD7 |

| 6 | К155ЛН1 | DD8 |

| 7 | КР537РУ17 | DD9 |

| 8 | К155ИД3 | DD10 |

| 9 | КР580ВВ51 | DD17 |

| 10 | КР580ВВ79 | DD18 |

| 11 | К155ЛИ6 | DD22 |

| 12 | К514ИД2 | DD25, |

| 13 | CD8-BW30R6-A11 | HL1 |

| 14 | Разъем последовательного интерфейса | XC4 |

Центральное процессорное устройство включает в себя микропроцессор ВМ80 в минимальном окружении дополнительных микросхем:

1) Тактовый генератор ГФ24, который синхронизируется кварцевым резонатором с частотой 18 МГц. Вход RDYIN подключен через сопротивление 1 кОм для формирования высокого уровня на этом выходе. Вход RESIN подключен к кнопке с нормально разомкнутыми контактами, RC цепь предназначена для формирования сигнала RESET в момент включения МПС и для защиты от дребезга контактов кнопки. В цепь кварцевого резонатора включена емкость 20 нФ для запуска генератора в момент подачи напряжения.

2) Буферные регистры АП5 предназначены для увеличения нагрузочной способности шины адреса (System Address Bus) микропроцессора.

3) Системный контроллер ВК28 формирует на своих выходах системную шину данных (System Data Bus) и шину управления (System Control Bus). Его входы STSTB, HLDA, WR, DBIN подключены к соответствующим выходам микропроцессора и тактового генератора. Вход BUSEN заземлен.

К сформированным шинам подключаются остальные контроллеры, а также модули памяти ПЗУ и ОЗУ. Выборку контроллеров осуществляют дешифраторы DD10, DD11.

В проектируемой МПС обслуживание прерываний осуществляет один контроллер ВН59. Он подключается к 8-разрядной системной шине данных (ШД), а также к шине управления (ШУ). Для адресной выборки внутренних регистров используется линия адреса А0 от шины адреса (ША). К входам IR0-IR7 подключаются контроллеры, которым необходимы прерывания. Так как каскадирования не требуется, поэтому инверсный вход SP/EN заземляется.

Формирование трех 8-битных двунаправленных интерфейса Port A, B, C осуществляет контроллер ВВ55. Его выводы подключаются к соответствующим линиям ШД, ША, ШУ. Данный контроллер работает в режиме M1, поэтому линии PA0-7 и PB0-7 работают ввод и вывод соответственно, а линии PC0-7 используются для управляющих сигналов.

Функции ввода с 128-клавишной клавиатуры и отображения информации на одном 8-разрядном цифровых дисплеях HL1 выполняет контроллер ВВ79. Для сканирования клавиатуры контроллер формирует двоичный код на линиях SL0-SL3, анализируя при этом состояние линий RL0-RL7. Преобразование двоичного кода в кодовые последовательности М0-М15 выполняет дешифратор столбцов DD24, DD27. Выходы этих дешифраторов подключены к разрядам 7-сегментных индикаторов, а также к линиям клавиатуры. Непосредственное управление индикаторами с общим анодом осуществляют дешифраторы К514ИД2, преобразующие двоичный код с линий PA0-PA2, PB0-PB2 в 7-сегментный код. Линии PA3, PB3 подключены напрямую на вывод H индикаторов, который относится к светодиоду десятичной точки. Вход S подключается к выходу BD контроллера для гашения индикаторов.

Заключение

В данном курсовом проекте была получена МПС на базе комплекта КР580. Данная МПС обладает относительно небольшим быстродействием. Она позволяет решать задачи, связанные с управлением разнообразными технологическими операциями. Разработанная система позволяет подключать устройства, которые требуют динамического изменения временных и частотных характеристик их входных сигналов. Присутствие в этой МПС программируемого параллельного интерфейса КР580ВВ55 предусматривает три канала, к которым можно подключать УВВ, обменивающихся 8-разрядными словами, а также позволяет гибко манипулировать этими каналами, изменяя их предназначение. КР580ВМ80 является микропроцессором с фиксированным набором команд, что облегчает составление программ. Объем ПЗУ позволяет записать достаточно функциональную программу, расширяя тем самым возможности данной МПС.

Список используемой литературы

1. Большие интегральные схемы запоминающих устройств: Справочник. – М.: Радио и связь, 1990.

2. Калабеков Б.А.. “Цифровые устройства и микропроцессорные системы”. Москва 2003г.

3. Г. И. Пухальский. “Проектирование микропроцессорных систем”. Санкт-Петербург 2001г.

4. Справочник, М.: Редакция, 1991 – 196 c. Интегральные микросхемы зарубежных стран и их аналоги производства СССР.

5. Интернет-сайт: http://www.computer-museum.ru.

6. Интернет-сайт: http://www.wikipedia.org.ru